- 来自日本东京科学研究所(Science Tokyo)的一组研究人员 conceptualised 一种创新的 2.5D/3D 芯片集成方法,称为 BBCube。传统的系统级封装(SiP)方法,其中半导体芯片使用焊点排列在二维平面(2D)上,存在尺寸相关的限制,需要开发新的芯片集成技术。为了高性能计算,研究人员通过采用 3D 堆叠计算架构开发了一种新型电源技术,该架构由直接堆叠的动态随机存取存储器上放置的处理单元组成,这是 3D 芯片封装的重大进步。为了实现 BBCube,研究人员开发了涉及精确和高速键合技

- 关键字:

2.5D/3D封装 工艺制程

- 来自日本东京科学研究所 (Science Tokyo) 的一组研究人员构思了一种名为 BBCube 的创新 2.5D/3D 芯片集成方法。传统的系统级封装 (SiP) 方法,即使用焊料凸块将半导体芯片排列在二维平面 (2D) 中,具有与尺寸相关的限制,因此需要开发新型芯片集成技术。对于高性能计算,研究人员通过采用 3D 堆栈计算架构开发了一种新颖的电源技术,该架构由直接放置在动态随机存取存储器堆栈上方的处理单元组成,标志着 3D 芯片封装的重大进步。为了实现 BBCube,研究人员开发了涉及精确和高速粘合

- 关键字:

2.5D/3D 芯片技术 半导体封装

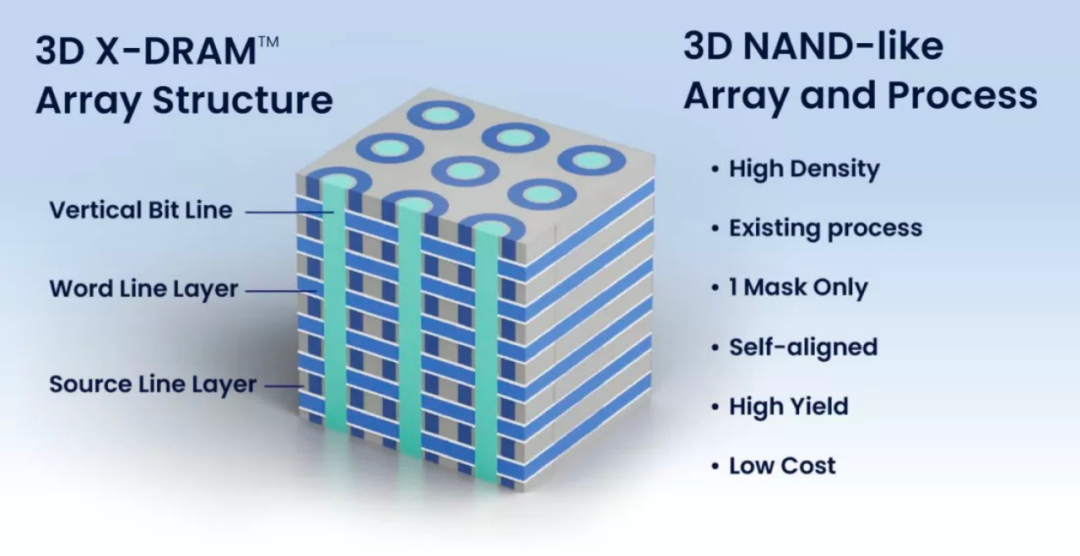

- 存储设备研发公司Neo Semiconductor Inc.(加利福尼亚州圣何塞)推出了其3D-X-DRAM技术的铟-镓-锌-氧化物(IGZO)变体。3D-X-DRAM 于 2023 年首次发布。Neo 表示,它已经开发了一个晶体管、一个电容器 (1T1C) 和三个晶体管、零电容器 (3T0C) X-DRAM 单元,这些单元是可堆叠的。该公司表示,TCAD 仿真预测该技术能够实现 10ns 的读/写速度和超过 450 秒的保持时间,芯片容量高达 512Gbit。这些设计的测试芯片预计将于 2026 年推出

- 关键字:

Neo Semiconductor IGZO 3D DRAM

- 12 月 6 日消息,博通当地时间昨日宣布推出行业首个 3.5D F2F 封装技术 3.5D

XDSiP 平台。3.5D XDSiP 可在单一封装中集成超过 6000mm2 的硅芯片和多达 12 个 HBM 内存堆栈,可满足大型 AI

芯片对高性能低功耗的需求。具体来看,博通的 3.5D XDSiP 在 2.5D 封装之外还实现了上下两层芯片顶部金属层的直接连接(即 3D 混合铜键合),同时具有最小的电气干扰和卓越的机械强度。这一“面对面”的连接方式相比传统“面对背”式芯片垂直堆叠拥有 7 倍的信

- 关键字:

博通 3.5D F2F 封装平台 富士通 MONAKA 处理器

- 随着半导体行业的快速发展,先进封装技术成为了提升芯片性能和功能密度的关键。近年来,作为2.5D和3D封装技术之间的一种结合方案,3.5D封装技术逐渐走向前台。什么是3.5D封装技术3.5D封装技术最简单的理解就是3D+2.5D,通过将逻辑芯片堆叠并将它们分别粘合到其他组件共享的基板上,创造了一种新的架构。能够缩短信号传输的距离,大幅提升处理速度,这对于人工智能和大数据应用尤为重要。不过,既然有了全新的名称,必然要带有新的技术加持 —— 混合键和技术(Hybrid Bonding)。混合键合技术的应用为3.

- 关键字:

封装技术 TSV 中介层 3.5D

- ● 占用空间小,性能强劲● 紧凑便携● 激光动平衡技术小型高性能复合轴承涡轮分子泵HiPace 10 Neo普发真空的新型HiPace 10 Neo涡轮分子泵是一款紧凑型真空泵。它便于集成在便携式设备中,尤其是分析仪器行业。得益于普发真空的激光动平衡技术HiPace10 Neo 是该系列历史上具有最小的噪音排放和极低的振动频率的一款产品。普发真空产品经理亚历山大·克鲁特(Alexander Kreuter)表示:“作为真空技术的领先供

- 关键字:

Neo 涡轮分子泵 普发真空

- 芯原股份近日宣布低功耗 AIoT 芯片设计厂商炬芯科技股份有限公司(炬芯科技, 股票代码:688049.SH)在其高集成度的双模蓝牙智能手表SoC ATS3085S和ATS3089系列中采用了芯原低功耗且功能丰富的2.5D图形处理器(GPU)IP。 炬芯科技的智能手表SoC ATS3085S和ATS3089系列拥有卓越的图形显示性能,采用2D+2.5D双GPU硬件加速配置,支持JPEG硬件解码,具有高帧率、低功耗等特点。该系列SoC以其高集成度,可实现单

- 关键字:

炬芯 智能手表 芯原 2.5D GPU IP

- 目前英伟达的H100等数据中心GPU都是由台积电(TSMC)负责制造及封装,SK海力士则供应HBM3芯片。不过人工智能(AI)的火热程度显然超出了大家的预期,导致台积电的先进封装产能吃紧。虽然台积电不断扩大2.5D封装产能,以满足英伟达不断增长的需求,但是英伟达在过去数个月里,与多个供应商就2.5D封装产能和价格进行谈判,希望能够分担部分工作量。据The Elec报道,三星已经获得了英伟达的2.5D封装订单。其高级封装(AVP)团队将向英伟达提供中间层,以及I-Cube封装。I-Cube属于三星自己开发的

- 关键字:

三星 英伟达 封装 2.5D

- 月 8 日消息,据韩国电子行业媒体 TheElec 报道,三星电子成功拿下了英伟达的 2.5D

封装订单。消息人士透露,三星的先进封装 (AVP) 团队将为英伟达提供 Interposer(中间层)和 I-Cube,这是其自主研发的

2.5D 封装技术,高带宽内存 (HBM) 和 GPU 晶圆的生产将由其他公司负责。据IT之家了解,2.5D

封装技术可以将多个芯片,例如 CPU、GPU、I / O 接口、HBM 等,水平放置于中间层上。台积电将这种封装技术称为

CoWoS,而三星则称之为

- 关键字:

三星 英伟达 AI 芯片 2.5D 封装 订单

- ● Neo NPU可有效地处理来自任何主处理器的负载,单核可从 8 GOPS 扩展到 80 TOPS,多核可扩展到数百 TOPS● AI IP可提供业界领先的 AI 性能和能效比,实现最佳 PPA 结果和性价比● 面向广泛的设备端和边缘应用,包括智能传感器、物联网、音频/视觉、耳戴/可穿戴设备、移动视觉/语音 AI、AR/VR 和 ADAS● 全面、通用的 NeuroWeave SDK 可通过广泛的 Caden

- 关键字:

Cadence Neo NPU IP NeuroWeave SDK

- 西门子数字化工业软件近日推出Tessent Multi-die软件解决方案,旨在帮助客户加快和简化基于2.5D和3D架构的新一代集成电路(IC)关键可测试性设计(DFT)。随着市场对于更小巧、更节能和更高效能的IC需求日益提升,IC设计界也面临着严苛挑战。下一代组件正倾向于采用复杂的2.5D和3D架构,以垂直(3D IC)或并排(2.5D)方式连接多个晶粒,使其能够作为单一组件运作。但是,这种做法为芯片测试带来巨大的挑战,因为大部分传统的测试方法都是基于常规的2D流程。为了解决这些挑战,西门子推出Tess

- 关键字:

西门子 2.5D 3D 可测试性设计

- 在燧原科技(燧原)发布云燧T10之际,燧原与格芯(GLOBALFOUNDRIES)近日共同宣布推出针对数据中心培训的高性能深度学习加速卡解决方案,其核心“邃思”(DTU)基于格芯12LP®FinFET平台及2.5D 封装技术,为云端人工智能训练平台提供高算力、高能效比的数据处理。燧原的“邃思”(DTU)利用格芯12LP FinFET平台拥有141亿个晶体管,采用先进的2.5D封装技术,支持PCIe 4.0接口和燧原 Smart Link高速互联。支持CNN/RNN等各种网络模型和丰富的数据类型

- 关键字:

FinFET 2.5D

neo-5d介绍

您好,目前还没有人创建词条neo-5d!

欢迎您创建该词条,阐述对neo-5d的理解,并与今后在此搜索neo-5d的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473