利用Virtex-5 FPGA实现最低功耗解决方案

过渡至65纳米工艺的FPGA具备采用更小尺寸工艺所带来的优势:低成本、高性能和更强的逻辑能力。尽管这些优势能够为高级系统设计带来激动人心的机会,但65纳米工艺节点本身也带来了新的挑战。例如,在为产品选择FPGA时,功耗的考虑变得越来越重要。很可能下一代设计会需要在功耗预算不变(或更小)的情况下,集成更多的特性和实现更高的性能。

本文引用地址:https://www.eepw.com.cn/article/84173.htm本文将分析功耗降低所带来的益处,还将介绍Virtex-5器件中所采用的多种技术和结构上的革新,它们能提供功耗最低的解决方案,并且不牺牲性能。

降低功耗的好处

低功耗的FPGA设计所带来的优势不仅是能满足器件工作的散热要求。虽然满足元件指标对于性能和可靠性十分重要,但如何实现这一点对于系统成本和复杂性都有着巨大的影响。

首先,降低FPGA的功耗使设计人员能够采用更便宜的电源,这样的电源使用的元件数量较少,并且占用的PCB面积也较小。高性能电源系统的成本通常为每瓦0.5到1美元。低功耗的FPGA直接降低了系统的整体成本。

其次,由于功耗直接与散热相关,低功耗使设计人员能够使用更简单、更便宜的热量管理解决方案。在很多情况下,设计者将不再需要散热器,或者只需要更小、更便宜的散热器。

最后,由于低功耗工作意味着更少的元件和更低的器件温度,因此将提高整个系统的可靠性。器件工作温度每降低10℃,就相当于元件寿命提高了两倍,因此对于需要高可靠性的系统而言,控制功耗和温度十分重要。

功耗:挑战和解决方案

FPGA(或任何半导体器件)中的总功耗等于静态功耗和动态功耗之和。静态功耗主要由晶体管的泄漏电流引起,即晶体管在逻辑上被关断时,从源极“泄漏”到漏极或通过栅氧“泄漏”的小电流。动态功耗是器件核心或I/O在开关过程中消耗的能量,与频率相关。

在缩小晶体管尺寸时(例如,从90纳米到65纳米),泄漏电流将会增大。新工艺节点所使用的短沟长和薄栅氧使电流更容易从晶体管的沟道区或通过栅氧泄漏。

在90纳米Virtex-4系列产品中,赛灵思公司使用了“三栅极氧化层”的工艺技术,向电路设计者提供了一种强有力的阻止漏电工具。在前几代FPGA中,使用两种栅氧厚度:薄栅氧用于FPGA核心中高性能、低工作电压的晶体管,而厚栅氧用于I/O模块中尺寸较大,需要承受大电压的晶体管。简言之,“三栅极氧化层”指增加一种中间厚度栅氧的晶体管,它的漏电比薄栅氧的核心晶体管要小得多。

“中间栅氧”的晶体管用在器件核心外围非关键性能的电路(像设置存储器)或不需要对变化的栅压进行快速开关响应的电路(像传输门)中。薄栅氧、漏电最大的晶体管只保留在需要快速开关速度的路径部分。结果,总的器件漏电大幅减小,同时性能比上一代FPGA有很大提高。

三栅极氧化层工艺使Virtex-4器件比竞争性90纳米FPGA在静态功耗上平均减少了超过70%。这一结果非常成功,因此Virtex-5系列产品中大量使用了这一技术,在65纳米工艺节点上降低漏电。

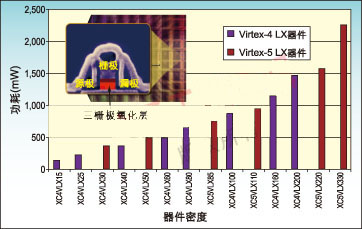

尽管业界预测65纳米器件的静态功耗将会大幅提高,但是图1显示了三栅极氧化层工艺使65纳米Virtex器件在最坏(温度最高)工作条件下达到了与尺寸相当的90纳米Virtex-4器件相同水平的静态功耗。因此,Virtex-5系列产品和竞争性高性能FPGA产品相比,在静态功耗方面具有真正的优势。

图1:Virtex-4与Virtex-5器件在85℃时的静态功耗比较。

动态功耗为65纳米FPGA带来一些其它方面的挑战。动态功耗的公式为:

动态功耗=C×V2×f

其中,C是总开关电容、V是电源电压、f是开关频率。65纳米工艺使FPGA的逻辑能力和性能比传统器件有了显著提高,也就是说更多的结点工作在更高的频率上。如果其它方面的条件不变,动态功耗将会增大。不过对于动态功耗而言,也有一个好消息:FPGA电源电压和结点电容通常在每一代新工艺中都会下降,从而使得动态功耗比上一代FPGA有所下降。

Virtex-5器件中,核心电源电压(VCCINT)从Virtex-4中所使用的1.2V下降到1.0V。由于寄生电容变小(与更小的晶体管相关),以及逻辑块间的互联线长度变短、电容变小,使结点电容减小。此外,Virtex-5器件在金属互联层之间使用了一种介电常数较低的材料。

Virtex-5器件的平均结点电容比Virtex-4器件大约减小了15%。加上电压降低带来的好处,至少相当于将Virtex-5器件的核心动态功耗降低了35~40%。

评论