- FPGA的应用越来越广泛,随着制造工艺水平的不断提升,越来越高的器件密度以及性能使得功耗因数在FPGA设计中越来越重要。器件中元件模块的种类和数量对FPGA设计中功耗的动态范围影响较大,对FPGA的电源功耗进行了分析

- 关键字:

FPGA 静态功耗 动态功耗 触发率

- 结合采用低功耗元件和低功耗设计技术在目前比以往任何时候都更有价值。随着元件集成更多功能,并越来越小型化,对低功耗的要求持续增长。当把可编程逻辑器件用于低功耗应用时,限制设计的低功耗非常重要。本文将讨论

- 关键字:

元件 动态 静态功耗 方法

- 图2.9举例说明了一个ECL或GAAS射极跟随器输出电路。该电路在HI和LO两个状态都有电流流过。对于10KH和10G产品系列,两者的逻辑HI和LO输出电压都是相近的,尽管不同的ECL和GAAS射极耦合逻辑系列在温度轨迹特性上存在细

- 关键字:

射极跟随器 静态功耗 输出电路

- 一旦推拉输出电路完全转换,静态功耗等于源电流乘以导通臂上的剩余电压。我们将分别计算出LO和HI状态下的功率,然后取二者的平均值。图2.6说明了理想的TT驱动器在LO和HI状态下的功耗。对于标准的TTL器件,Q2处于饱和

- 关键字:

推拉输出电路 静态功耗

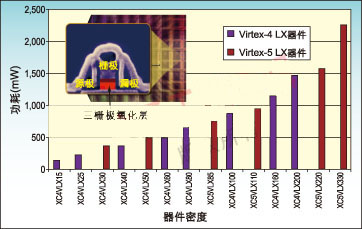

- 过渡至65纳米工艺的FPGA具备采用更小尺寸工艺所带来的优势:低成本、高性能和更强的逻辑能力。尽管这些优势能够为高级系统设计带来激动人心的机会,但65纳米工艺节点本身也带来了新的挑战。例如,在为产品选择FPGA时,功耗的考虑变得越来越重要。很可能下一代设计会需要在功耗预算不变(或更小)的情况下,集成更多的特性和实现更高的性能。

本文将分析功耗降低所带来的益处,还将介绍Virtex-5器件中所采用的多种技术和结构上的革新,它们能提供功耗最低的解决方案,并且不牺牲性能。

降低功耗的好处

- 关键字:

FPGA 低功耗 Virtex-5 静态功耗 动态功耗

- Actel 公司宣布推出业界最低功耗的现场可编程门阵列 (FPGA) -- IGLOO™ 系列。这个以 Flash 为基础的产品系列的静态功耗为5µW,是最接近竞争产品功耗的四分之一;与目前领先的PLD产品比较,更可延长便携式应用的电池寿命达5倍,因而奠定了低功耗的新标准。 由于便携式产品的生命周期短及市场竞争激烈,设计人员必需不断增加新的功能和复杂性,但却不能耗用

- 关键字:

Actel FPGA 单片机 静态功耗 嵌入式系统 通讯 网络 无线

静态功耗介绍

您好,目前还没有人创建词条静态功耗!

欢迎您创建该词条,阐述对静态功耗的理解,并与今后在此搜索静态功耗的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473