用FPGA实现多路PWM输出的接口设计与仿真

3 逻辑仿真和器件验证

行为级仿真是在HDL源代码设计完成之后,通过设计测试平台文件(激励和测试矢量)来验证设计的正确性。逻辑仿真是在逻辑综合之后,对生成的门级网表进行验证。测试平台文件与采用行为级仿真的测试平台文件,这样能够保证设计验证的一致性。并且,逻辑验证是一种理想的门级网表,不存在延时信息。器件验证也称版图后仿真,它是在FPGA实现之后,提取出门级网表和延时信息进行验证,测试平台文件与行为级一样。器件验证结果是比较接近真实硬件的结果。完全通过这3层的验证,基本上可以保证设计的结果与测试平台文件一致。

行为仿真和器件仿真也可直接在QuartusⅡ中进行,其中输入激励波形和输出观察节点在QuartusⅡ波形输入窗口进行设置,在设计通过功能仿真后,需要进一步选择器件仿真以验证设计的正确性。器件仿真时包含了所选择的对应FPGA估算延时或实际延时信息,故仿真速度较功能仿真慢很多。通过仿真可以及早发现设计中的错误,并根据具体情况进行修改,包括修改硬件实现架构、设计代码、约束条件等一个或多个方面。器件仿真通过后,则可以将设计下载到芯片,进行硬件功能验证。

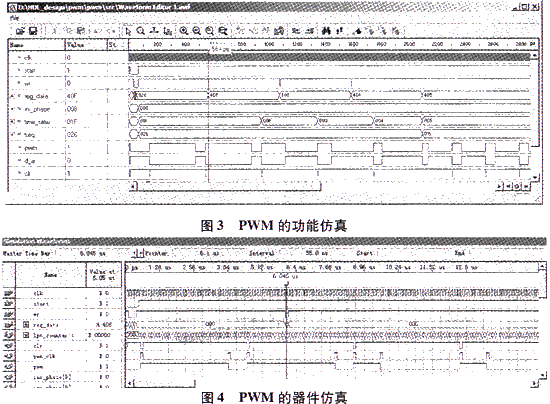

图3是对应PWM的功能仿真结果波形。从图3中可以看出,在564 ps时刻CPU向PWM写入新的控制常数后,下一个周期的PWM输出占空比立刻发生了相应改变。

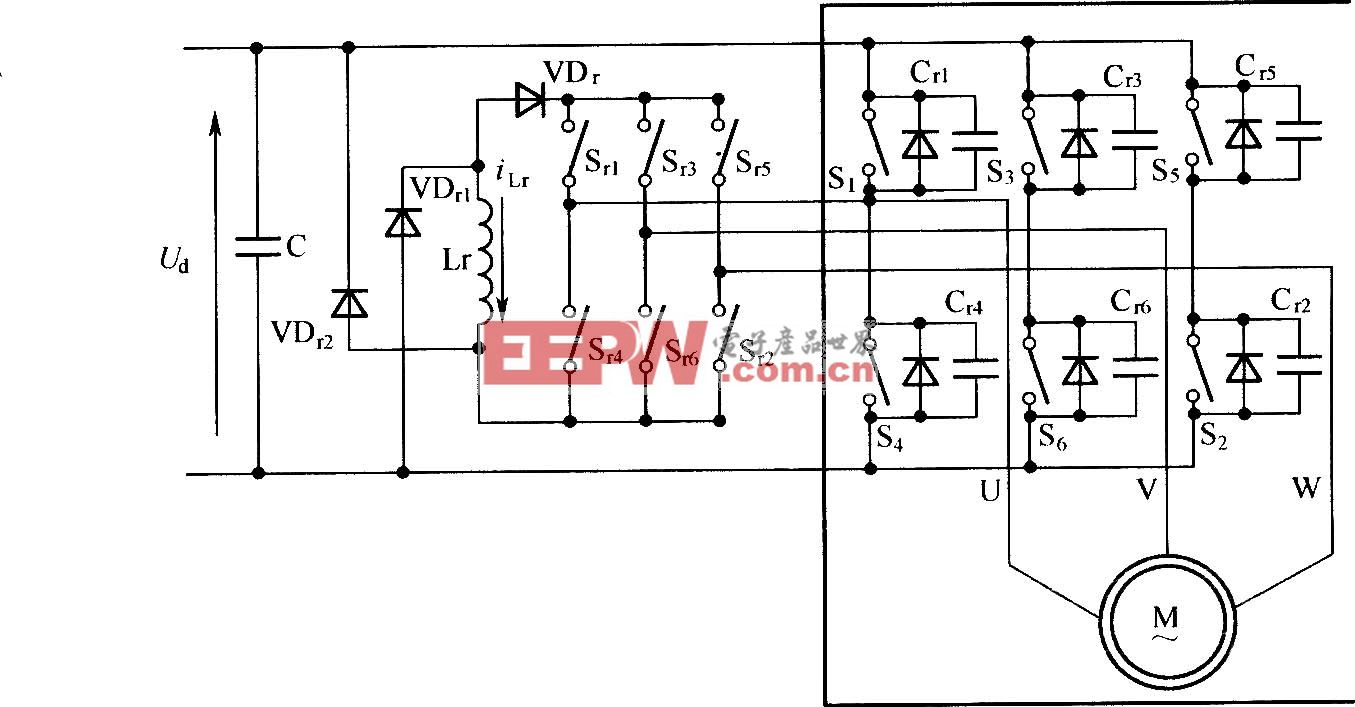

图4是相应设计在QuartusⅡ下编译通过后进行器件仿真的波形,由图4可见,其时序功能正确。通过器件下载编程方法下载到相应的FPGA,就可以结合整个嵌入式系统进行硬件调试。

4 结束语

在FPGA开发软件中完成设计以后,软件会产生一个最终的编程文件,QuartusⅡ中是.pof或.sof。现在的FPGA基本都采用在系统编程方式,对于EEP-ROM/Flask/SRAM工艺的在系统可编程FPGA,厂家提供编程电缆,如Altera公司提供的下载电缆类型有ByteBlasterⅡ并口下载电缆、USB BlasterTMUSB口下载电缆、MasterBlaster 通信缆线(USB或RS-232端口)等,其配置方式可以有主动/被动串行配置方式、JTAG方式等。电缆一端装在计算机的相应接口上,另一端接至PCB(印制电路板)上的编程插头,它向系统板上的器件提供配置或编程数据,这就是所谓的ISP(在线系统编程)。

在电机控制等许多应用场合,需要产生多路频率和脉冲宽度可调的PWM波形,本文通过使用Altera公司FPGA产品开发工具QuartusⅡ,设计了6路PWM输出接口,并下载到FPGA,实现与CPU的协同工作。在嵌入式系统中通过FPGA扩展系统功能的设计是一种有效的方法。

pwm相关文章:pwm原理

评论