基于最佳接收的UART的设计与实现

在嵌入式系统设计中常使用通用异步接收和发送器UART(Universal Asynchronous Receiver/Transmitter)实现系统控制信息或低速数据信息的传输,而UART所采用的奇偶校验方式不具备前向纠错能力,检错能力也有限,所以在设计UART时要尽可能提高其抗干扰能力,以加强系统的可靠性。

本文引用地址:https://www.eepw.com.cn/article/83208.htm1 基于最佳接收的UART

目前UART中的接收器多采用如图1所示的设计。

同步模块的作用是检测异步串口的同步位(Sync位)并提取抽样判决需要的采样信号,使抽样判决模块尽量在输入信号RXD的码元中部对信号采样(如图2)。因为信号在码元边沿跳变时会有振铃或过冲等抖动,所以码元的边沿部分不适合采样。要想获得较佳的抽样判决效果,最好在靠近码元中部的位置对接收到的信号进行抽样判决。

这种在码元中部进行抽样判决的接收方法可以有效去除振铃、过冲等信号的边沿抖动带来的影响,但无法解决随机脉冲干扰带来的问题。如图3所示,随机脉冲干扰可能在任何时刻出现。即使同步模块工作正常,使得抽样判决总处在码元中部的最佳采样时刻,也有可能由于随机脉冲干扰造成判决错误。

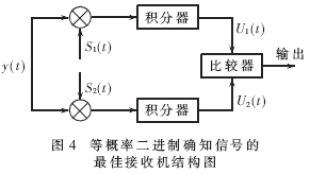

为了尽可能地减弱随机干扰及其他干扰给信号接收带来的影响,引入最佳接收机结构来设计UART的接收器,以实现信号的最佳接收。等概率二进制确知信号(异步串口通信的信号即属于此情况)的最佳接收机结构如图4所示。

图4中的乘法器和积分器实质上构成了一个相关器,因此上述结构又称为相关器形式的最佳接收机。其中相关器的输出u(t)由下式定义:

其中:T为采样周期,N表示一个码元的时间包含N个采样周期。

U1(kT)和U2(kT)由上式计算可得,然后送到比较器在最佳判决时刻(t=kNT)进行比较,若U1(kT)≥U2(kT),则判决为逻辑1,否则判决为逻辑0。

UART接收器接收的信号是未经调制的二进制基带信号,码元波形不是高电平就是低电平,两种码元的波形截然不同。因此,如果输入信号Y(nT)与S1(kT)相关运算的结果较大,则Y(nT)与S2(kT)相关运算的结果就很小;反之亦然。所以可以将上述最佳接收机结构中S2(kT)这一路相关器省略,只保留一路相关器。最后的比较器改成判决器,判决准则是:如果相关器在最佳判决时刻(t=kNT)的输出大于某个阈值,则判决为逻辑1;否则判决为逻辑0。经过简化改进基于最佳接收机结构的UART接收器的框图如图5所示。

下面以一个简单示例证明基于最佳接收的UART接收器可以有效地去除随机干扰给信号接收带来的影响。如图6所示,在这个码元周期内,如果采用一次抽样判决,则即使处于一次抽样判决的最佳采样时刻,也会由于随机脉冲干扰而产生误判;如果引入数字相关器在最佳判决时刻进行判决,则尽管由于信号边沿的抖动和随机脉冲的干扰,信号的波形遭到了破坏,但信号在码元周期内相关运算的结果为7,大于阈值5,接收器依然能正确地判定接收到的信号为逻辑1。这将有效抑制随机干扰给信号接收带来的影响。

2 基于FPGA的UART设计优化

数字相关器的引入,极大地提高了UART接收器的抗干扰性能,但也带来了两个问题:

(1)在数字相关器输出相关运算的结果后,判决器需要在最佳判决时刻进行判决,因为此时与信号的相关输出最大。同步模块得到的判决信号与这个最佳判决时刻的偏移越大,UART接收器的性能就越差。也就是说,数字相关器对同步模块的判决信号有很高的精确度要求。

(2)数字相关器是一个运算量相当大的复杂逻辑器件。

以上两个问题使得UART接收器的逻辑结构非常庞大,并将耗用很大的逻辑资源。而在大多数嵌入式系统应用中,UART通常只是控制信息的一个接口,如果设计出来的UART的IP本身就占用了大量的逻辑资源,则使用者肯定不能接受,且这样的UART的IP核也毫无价值。所以,要使得这种高性能的UART能在实际工程中应用,就必须优化UART的逻辑设计,减少耗用的资源。下面将以现场可编程逻辑门阵列FPGA(Field Programmable Gate Array)为设计平台,根据UART接收器中同步模块和数字相关器的结构特点以及FPGA的结构特点,对逻辑设计进行优化。

2.1 同步模块的设计优化

UART的同步模块主要检测Sync位并得到判决信号。理想情况下,如果在一个码元内有N次采样,则当N次采样的结果都为0时,表明检测到一个Sync 位,而且此时就是数字相关器的最佳判决时刻(如图7)。可是由于信号的边沿抖动或是随机脉冲干扰,N次采样的结果通常无法达到同时为0的理想情况,如果以 N作为检测同步的门限,则可能检测不到Sync位,造成漏同步。

评论