基于SOC中处理器核的串扰故障激励检测

使用SBST进行故障检测时的系统基本要求

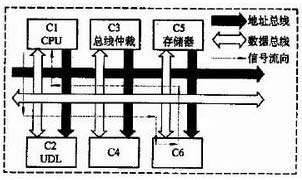

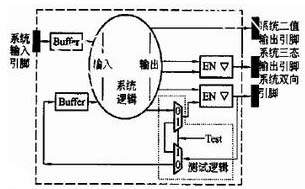

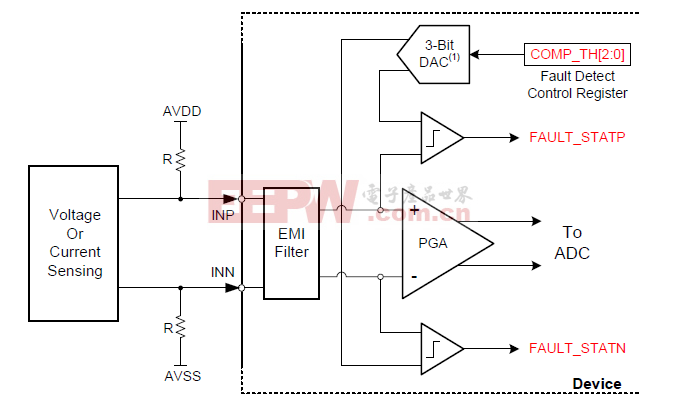

本文引用地址:https://www.eepw.com.cn/article/82152.htm典型的SOC系统由若干IP核、用户定义逻辑(UDL)以及核间互联总线组成,其原理图如图1所示。为了对SOC中IP核间互联总线进行串扰故障的激励检测[1~3],在使用基于软件的自测试(SBST)方法时,由处理器核(CPU)产生测试矢量并对被测总线施加激励,要对CPUC6核间的互联总线进行故障测试时,要求的测试矢量的流向如图1中的点线箭头所示。由图1中所示施加激励矢量的过程可以看出,测试矢量流经被测总线,在测试矢量到达终端C6时,为了对测试响应进行分析,此时要求进入C6的矢量和通过C6后的输出的矢量不因C6的存在而改变,这就要求C6具有透明(Transparent)的特性。对于符合IEEE1149.1测试标准的IP核,可以使用标准中规定的公开指令EXTEST通过Capter-DR,Shift-DR,Updata-DR等控制状态使系统引脚的输入和输出一致。但这种方法要经过一个串行移位的过程,故使得总体测试时间较长,成为测试效率提高的瓶颈。为此本文提出了一种改进方案,以下以双向脚为例进行说明,其示意图如图2所示。由图2中可以看出,为了使得IP核在进行系统总线串扰故障激励检测时具有透明的特性,在IP核的原始输入端和输出端之间加入了两个多路选择器,通过测试控制信号Test的作用使其在测试和正常工作状态之间转换,当Test=0时,IP核处于正常的工作状态,输入信号通过MUX1进入系统逻辑,经过处理后的信号通过MUX2直接输出,即此时的信号的通路为Input→MUX1→系统逻辑→MUX2→Output;而没有经过这种改进时的信号通路为Input→系统逻辑→Output,可以看出,改进后IP核的信号通路中只是多通过了两个多路选择器,故对IP核的正常工作几乎没有影响。当Test=1时,IP核处于总线测试状态,此时的信号通路为Input→MUX1→MUX2→Output;而没有经过这种改进时的信号通路同样为Input→系统逻辑→Output,此时可以看出,改进后IP核在系统总线处于测试状态时的信号通路中使用两个多路选择器代替了原有的系统逻辑,这在保证信号不变性的同时也极大地提高了系统总线的测试速度,而实现这一目标的代价是微小的。

图1 典型的SOC系统

图2 IP核的透明化方案

渐进式串扰故障激励检测模型

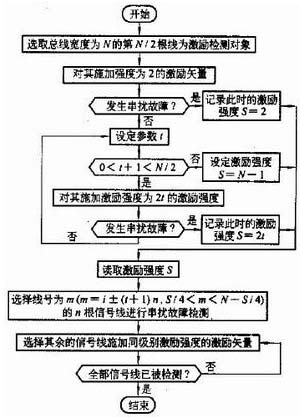

渐进式串扰故障激励检测模型的基本思想为:在对系统芯片IP核间互连总线进行串扰故障激励检测时,首先使用低强度级别的激励矢量,级别越低,同一组激励矢量可同时用于检测越多的不同传输线的串扰故障,如果在低级别时没能检测出串扰故障则由低到高增强激励矢量,直到发现串扰故障或最高级别的激励矢量已施加。该模型的思想是一个不断增强激励的渐进式过程。渐进式串扰故障激励检测模型既可以保证串扰故障检测的覆盖率,同时也可以提高检测的效率。使用该模型进行串扰故障激励检测的流程图如图3。

图3 渐进式串扰故障激励检测模型

渐进式串扰故障激励检测模型所需的激励检测矢量和检测对象的总线宽度、激励强度有关。设串扰故障激励检测的对象为N线并行传输线系统,其中N为偶数,对N为奇数的情况可以进行类推;设使用第2k级强度的激励矢量可以检测出其串扰故障发生,可同时检测出有串扰故障的传输线的个数为n,则

n=N-(n+1)k。

得到最终的表达式为

n=[(N-k)/(k+1)] (1)

对式(1)中的取整是为了保证激励的强度取高级别。

由式(1)可以看出,使用两个串扰故障激励矢量可以同时对n条传输线的串扰故障同时进行激励检测,且n和并行传输线的个数N成正比。对于N线并行传输线系统,测试所有传输线的所有类型的串扰故障(gp,gn,df,dr)所需的测试激励矢量数t=6[N/n]取上整数。

设激励强度级别为2,被测总线的宽度为8,则使用渐进式串扰故障激励检测模型所需的激励矢量的个数为18个。

基于软件的自测试(SBST)过程

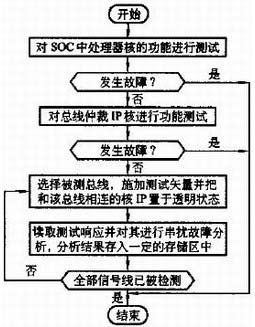

使用SBST方法对IP核间互联总线进行串扰故障激励检测时,根据一般SOC中都含有处理器核这一事实,利用其具有的处理和计算能力产生串扰故障的激励矢量,并对测试响应进行分析。这里产生的测试矢量是渐进式串扰故障激励检测模型所需的,系统中IP核中和被测总线相连的引脚都经过了透明化的改进,在这两个前提下,IP核间互联总线的SBST测试过程如图4所示。

图4 IP核间串扰故障激励检测流程图

由以上的使用SBST进行串扰故障激励检测的过程可以看出,由于SBST测试方法是以处理器核为基础的,因此在进行串扰故障激励检测前要确保处理器核本身的功能完全正确,同时由于要测试的对象为IP核间的互联总线,而不同总线连接是通过系统的总线仲裁IP核来完成的,因此其在总线串扰故障测试过程中也要确保功能正确。在有了这两个前提的基础上,就可以使用SBST方法进行各个IP核间互联总线的串扰故障激励检测,测试分析的结果可以存储在固定的存储区中用于测试后的分析。

针对以上提出IP核透明化处理所需的额外硬件开销问题,使用VerilogHDL语言对其进行了参数化的描述,其中是以和被测总线相连的引脚数为参数,使用仿真工具Verilog-XL对该描述进行了功能仿真。

仿真结果表明,使用SBST方案进行串扰故障的激励检测具有测试实时性、所需额外硬件开销少、测试效率高以及无需IP核内部结构信息等特点。同时,因为施加的测试矢量是渐进式串扰故障激励检测模型所需的测试矢量,故其对串扰故障的检测率为100%。这使得这种测试方案的性价比很高,因此其应作为众多测试方案中的首选。

评论