选择和表征锁相环在定时和相位控制中的应用

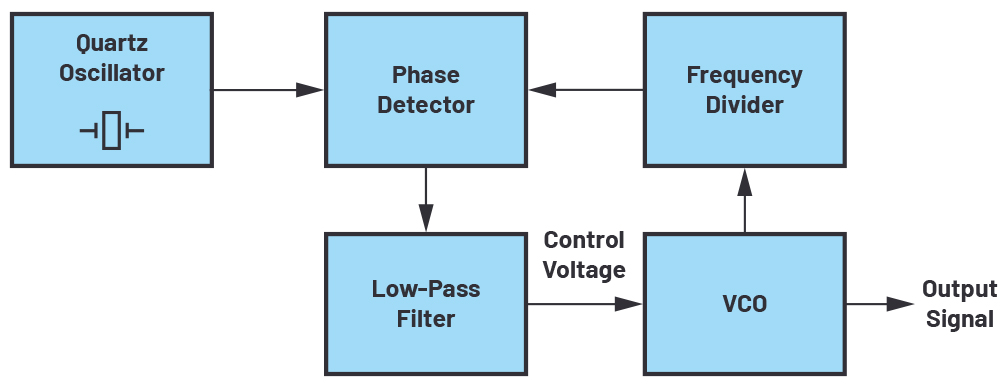

锁相环(PLL)广泛应用于无线通信,在基站中的主要用途是为发射器和接收器中的上变频和下变频电路提供一个稳定的、低噪声的射频(RF)本地振荡器(LO)。鉴于PLL本身的性能,它还可以用于控制其他许多电路中时钟信号的定时,而且在某些应用中,如果使用得当可以代替价格较贵的定时芯片。

本文引用地址:https://www.eepw.com.cn/article/80469.htm大多数高速数字电路的设计工程师会在注重相位的应用中选择很贵的定时芯片,因为通常都是对限定频率范围(通常是适合SONET/SDH频率的线路速率)粗略地表征定时指标。相比之下,PLL器件通常覆盖了很宽的频率范围,而且在相位控制或定时应用方面通常没有具体的规定。部分原因是由于采用无限多的输入和输出频率,而且对它们进行多种可能的倍频和分频比的组合。因此其相位延时特性很少有人研究,而且在PLL技术资料上几乎从来没有发表过。下面推荐了适合各种特定应用的PLL器件的特性,因为不同的应用需要不同的配置和需求,这可能会提供不同的结果。为此,本文将介绍在特别注重相位控制的应用中为表征PLL器件性能所采用的大量研究和实验的方法和结果。

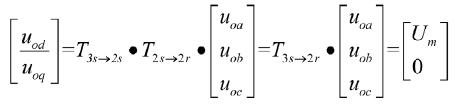

两个不同器件之间的相时延

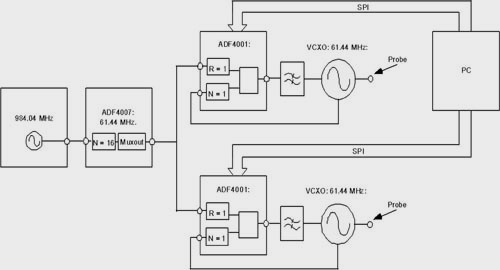

PLL的初始特性包括用相同参考时钟驱动的两个PLL器件的两个压控振荡器(VCO)输出信号之间的相位滞后的分析。这样做是因为如果不同器件的Ref到RF的传播延时偏差很大而且不可预知的话,由此得出结论在相位控制应用中采用PLL器件实际上是受限制的。最简单的配置就是采用PLL和外置的VCXO。低频的PLL可以采用ADI的ADF4001,对于ADF4001,参考(R)和反馈(N)分频系数都设为1。这样实际上就意味着PLL可以用作时钟清除电路,这时PLL器件的一种常见应用,电路连接如图1所示。

为了确保两个器件的参考计数器在尽可能多地相同时间里进行时钟控制,需要采用一种低噪声、短上升时间的方波。为了获得这样的方波,采用一种高频的分频器将984.04 MHz的正弦波经过16分频,输出一个61.44 MHz的高转换速率的方波。特别重要的一点是保证通过每个PLL的信号从分路器到各器件Refin引脚的传输距离应该完全相同。这样才能保证时钟脉冲以完全相同的时序对两个器件严格定时。更进一步的考虑就是确保两个PLL器件的计数器都在同一时刻复位。可以先将预设的内容写入PLL寄存器,然后同时将两器件的片选(CE)置成高电平以启动两颗芯片完成同时复位。这项功能也可以采用软件的计数器复位功能来实现。

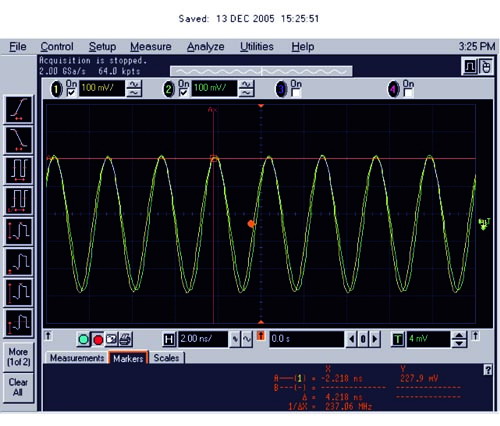

为了保证测量的精度,采用了有源的示波器探头(P6243)和一个高频数字示波器(TDS3054)。这样,在很大程度上保持了方波的形状而且有助于两个波形之间的比较。在示波器上显示的波形示出了两个几乎完全相同的输出信号之间有60 ps的偏差。

完成这种测量的另一种方法就是采用增益和相位检测器来测量两个不同信号之间的增益和相位差。在本实验中,两个PLL的VCXO输出都送至增益和相位检测器的输入。同样还要注意保证用于传送两个RF信号到增益和相位检测器输入端的电缆长度应该完全相同。结果相位输出端的信号输出是1.85 V,它超过了产品技术资料中提供的相当于0°相位误差的1.8 V预期等效值。

图1 相时延电路设置

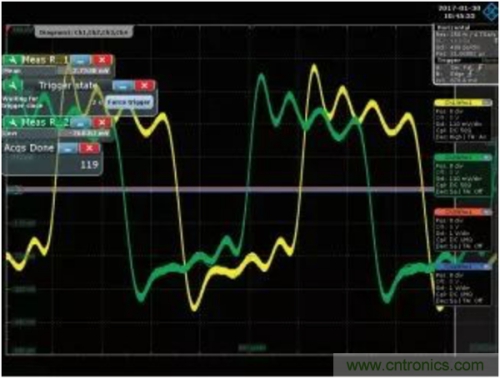

图2 由同相参考时钟驱动的两片ADF4360-7器件的RFoutA输出

Ref到RF的相时延

如果已经确定不同PLL器件之间从Ref到RF的传播延迟是类似的,那么下一步的工作应该确定Ref和RF VCO 输出信号之间的相位关系。人们希望Ref到RF的延迟很低,因为这样可以更容易地在时钟清洁和时钟分配电路中使用器件。

在本实验中,选用了一种带集成VCO的单芯片整数N分频 PLL数字频率合成器。该器件ADF4360-7采用一种类似于ADF4001的PLL,但是增加了双极性前置分频器(它能增大频率范围和分频系数)以及一个集成的内置VCO。本实验也可以用外部的VCO器件来实现,但是VCO输出和反馈N分频器之间的印制线长度会影响其相位关系。这个参数对于像ADF4360-7这样的集成PLL来说是无关紧要的,因为VCO实际上紧邻反馈计数器。

可以采用高转换速率的方波作为参考时钟,这时PLL用作时钟倍频器,从而将20.48 MHz输入整数倍频到491.52 MHz,同时再对这个输出进行2分频得到245.76 MHz的输出。为了获得2.56 MHz的鉴相器(PFD)频率,利用R计数器对20.48 MHz的信号进行8分频。采用高PFD允许使用较小的N值,这对邻近相位噪声是最有利的,因为参考时钟的任何噪声都会被放大20 log(N)倍,总的反馈系数为192。为了进行测量,采用和前面实验一样的设备,但是测量时要尽可能地靠近Ref和RF引脚。输入到输出的相时延是非常小的(<140 ps),实际的延迟可能小于用示波器测量到的值。这个延迟值随着温度的升高而增大,并且随温度的降低而减小(有时候低于0 ps)。电源电压也会造成类似的变化,但是采用这种配置的实验已经表明在3.0~3.6 V电源电压范围和-40℃~+85 ℃温度范围延迟变化总在±500 ps范围内。

对于带有内置VCO的两个单芯片整数N分频 PLL频率合成器,为了提供400 MHz的输出频率重复第一个实验。采用增益和相位检测器示出两个信号之间的延迟在相位检测器可示的范围内是同相的。高速示波器波形(见图2)基本上证实了这一点。波形中的异常是因为输出元件的失配,它影响到输出功耗。但是,对波形峰值的进一步分析表明信号基本上是同相的。

建议应用

ADF4360-x系列提供差分输出。采用增益和相位检测器已经证实这些输出具有180°的相位差。用两片ADF4360-x器件能够产生正交的LO信号,其中一片相对于另一片提供具有90°相位差的参考频率。第一片PLL可提供与其VCO有0~180°相位差的输出信号,而第二片器件可以产生90~270°相位的信号。这可以用于具有4个独立模数转换器(ADC)的高频采样应用中,利用四个不同相位的输出分别为每个ADC提供编码时钟。这样仅采用一片ADC就可以有效地将采样速率提高到原来的4倍。

结论和深入工作

ADI公司的ADF4xxx PLL适合用于相位控制应用中。频率越高的偏差越难表征,因为电缆长度和传播延迟的影响都比较重要。但是一般说来,结果是可预测、稳定和可重复的。

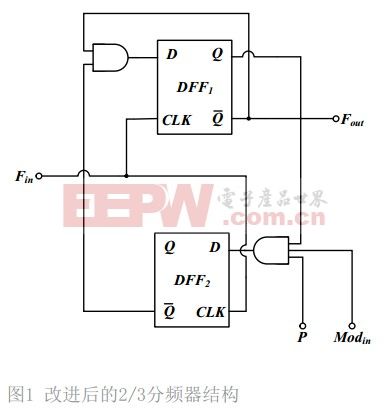

分频器相关文章:分频器原理

评论