ARM迎接新处理器架构:成败无非是重头再来

继先前将CoreLink CCI-500连结器应用在Cortex-A72核心架构设计,ARM稍早宣布推出全新CoreLink CCI-550连结器,并且加入多核心多丛集配置功能,预期下一波处理器核心架构可能同样导入多丛集 (Cluster)运作模式,亦即将如同联发科Helio系列处理器所主推“多档”运作模式。

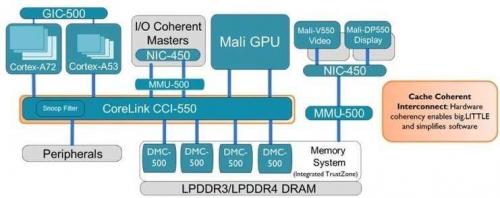

本文引用地址:https://www.eepw.com.cn/article/282166.htm根据ARM公布消息,新版CoreLink CCI-550连结器加入主动侦测核心运作资料改变时,并且强化资料存取缓冲频宽,将可在处理核心运作资料改变时,强化运算资料同步连结效率。此外,CoreLink CCI-550连结器将增加至连结六组处理器核心设计,架构上也能连结源自Mali GPU运算资料,藉此实现GPGPU平行运算效果,预期下一代“Mimir”Mali GPU便会支援此项设计。

而因应加入最多可连结六组处理器核心,CoreLink CCI-550连结器也加入支援最多六组记忆体通道 (对应32-48位元定址)、六组ACE主控连接埠等设计,同时提供最大频宽可提升60%、资料运算延迟表现降低20%,此外也能进一步降低处理器运算耗电量,并且透过平行运算方式增加整体效能,对于手机、数位电视等较耗电能产品均可达成省电目的。

此外,ARM在CoreLink CCI-550连结器端也导入DMC-500动态记忆体控制器,将支援LPDDR3-2133与最高LPDDR4-4267记忆体规格,并且提升27%记忆体频宽,同时降低25%处理器资料运算延迟率,本身也导入ARM TrustZone技术与DFI 4.0 PHY介面工业规范。

目前CoreLink CCI-550连结器、DMC-500动态记忆体控制器均预计在2016年下半年间问世,预期ARM也准备公布全新处理器核心架构设计。

评论