DSP推动3G移动通信革命

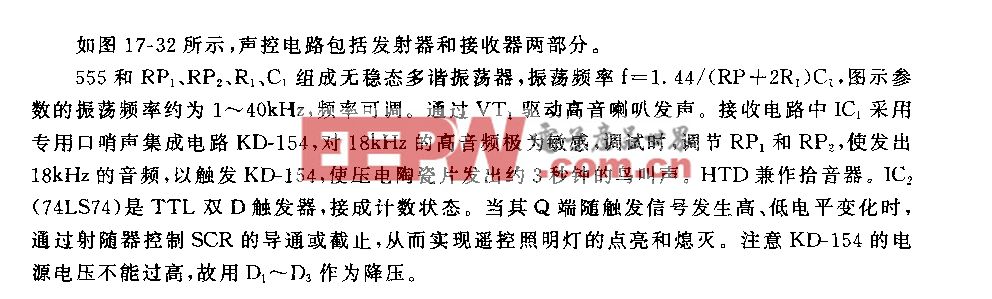

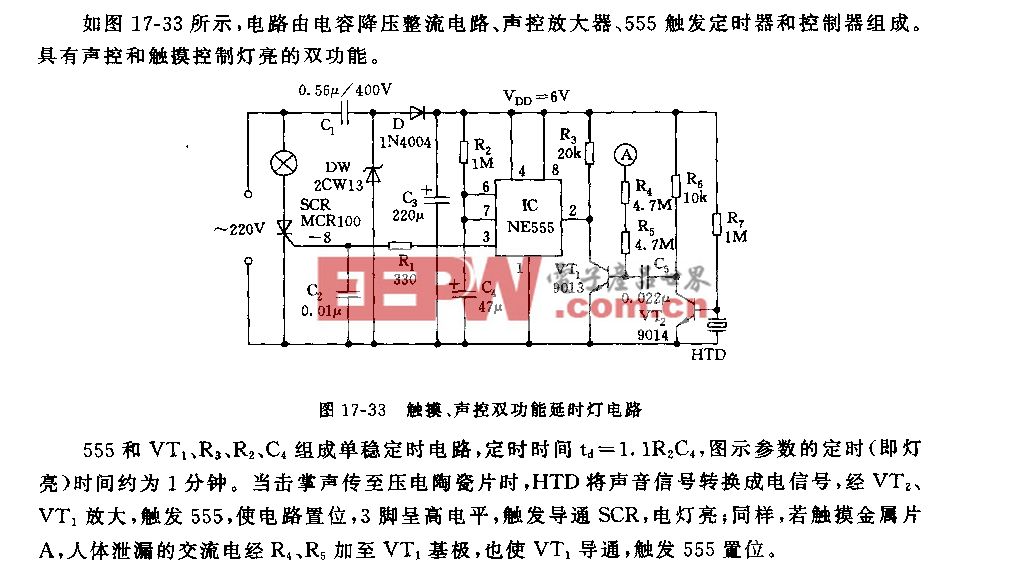

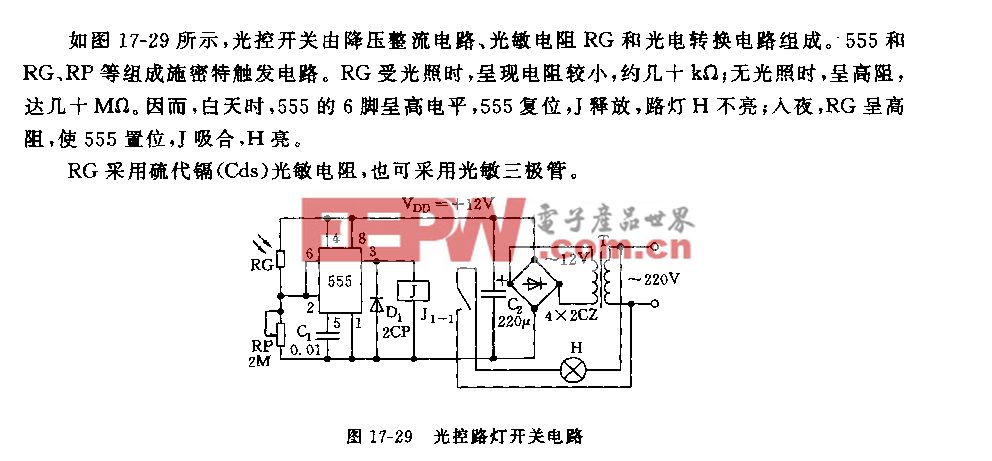

新近涌现的各种数字信号处理器(DSP)的规格尺寸繁多,外形各式各样,令人难以胜数,其设计目标也是为了满足各种对性能要求高低不同的应用。这些需求既包括附加在现有的处理器上、用于提供DSP功能的简易编码器,也包括可以驱动整个第三代蜂窝式电话的高性能器件。

本文引用地址:https://www.eepw.com.cn/article/2809.htm早期的DSP主要用于数学运算。但后来它们的应用大大拓宽。其结果是,现在DSP也应用于以前专属于微控制器的那些领域。在这些应用中,DSP所作的工作要比微控制器在同一领域中要重得多,因为系统现在靠一个处理器(DSP)工作,而非两个处理器(DSP/微控制器组合)。

设计者也在改进其编写代码的方式。例如,现在有多种途径可以实现一种特定的函数(如FFT)。处理器输入数据,进行处理然后再输出数据。两种不同的算法可以产生相同的结果,但途径不同,对运算能力的要求也大相径庭。随着工具的改进和设计者越来越适应DSP技术,这一现象也将得到改善。

由于DSP不象传统的微处理器和微控制器的应用环境那样成熟和确定,零售商就必须提供一揽子服务,包括软件和开发工具,而不仅仅是芯片本身。这就是DSP供应商有别于其他供应商的一个方面——给系统设计者提供所需的全套软件和工具,而不是把客户推给第三方。在方便设计者的同时,这样做也可以缩短基于DSP的产品推向市场的时间。

ARC是给现有产品添加一定程度DSP功能的多家厂商中的一家,只是所采用的方式有所不同。该公司提供了一个可定义的内核,而不是无法改动的硅片。用户使用可定义的核时,可以将其拆散,并按完全不同的体系结构重组。因此,当一个设计者决定在他的处理器中添加DSP功能时,最终获得的处理器从根本上来看将是全新的。

在使用一个固定的(如具有ARM或MIPS核)处理器时,添加DSP功能就要改变现有的体系结构,这就要求设计者学习新的软件或工具。因此,这些厂商有必要与现有的技术保持一致。因为在ARM或类似的产品中,设计者对开发工具及其达到的性能水平已经熟悉和适应。但这也从根本上限制了设计,你不论添加什么,只能放置在核的外围。真正的关键在于DSP协处理器(如果这是实现的方式)和主核间的带宽。

用PLD(可编程逻辑器件)以搭积木的方式也可以实现DSP。在这种方法中,固定的功能一般下载到芯片中。这些功能可包括FIR 滤波、FFT和纠错。显然,PLD的功耗比传统的DSP更多,但从所获得的灵活性来看也是一种不错的选择。

Altera 公司的一位产品市场高级经理Justin Cowling说:“用一个PLD构建的DSP IP核可以取代电路板上的多个DSP,当你谈论把几个DSP放到电路板上时,功耗明显高于单个PLD。我们已经建立了一个很大的功能固定的DSP功能库。当一个客户设计一个系统时,他只需画一个包含多个DSP功能的方框图。”

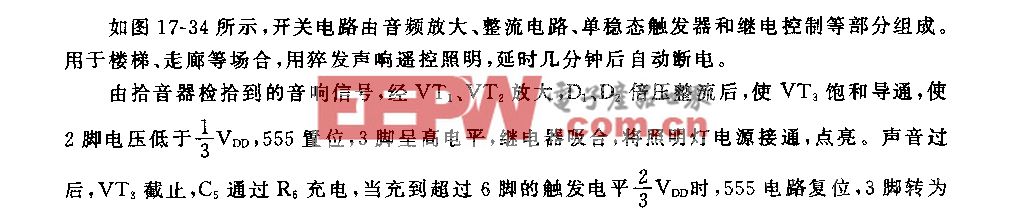

添加DSP IP对LSI Logic公司的工作人员来说是很自然的事。该公司提供低功耗的可以集成到一片ASIC中的DSP核。CW3000和CW3001两种核均基于LSI ZSP400体系,分别在95和152MHz两种频率下工作(图1)。ZSP400是一种完全静态的核,可以接受高级时钟管理和低功耗工作模式。这些低功耗模式使得非关键的外围设备和系统时钟可以采用软件或外部中断控制,而时钟管理允许核在逐个周期基础上避开无效逻辑的时钟控制。

这种基于核的方法的优点在于开发者明白DSP核提供完全兼容的集成后,可以用符合ZSP标准的产品制作样机。通过采用一个标准的系统总线(AHB),ASIC开发者可以选择多种处理器, 如MIPS和ARM。

Analog Devices 公司(ADI)最近发布了一种属于高端的DSP产品。所推出的Blackfin系列处理器基于一种特殊的核,而该核与Intel公司的产品一前一后推出。ADI宣称这种核在DSP运算性能和功耗方面取得了突破。该系列处理器瞄准了“混合产品”,即组合了通信和运算功能的系统。系列中的第一款21535目前正在进行样品展示。ADI认为,其优势之一是有该公司的无线研发小组参与开发。这两类研发小组的“杂交”应该能加快此类混合产品的推出。

Blackfin产品采用了动态功耗管理。这意味着在运行中可以调整频率和电压,以使性能和电池寿命最优化。为了增强动态功耗管理,ADI开发了用于调节DSP电压和频率的芯片组。在核方面,ADI试图很快将Blackfin技术的处理能力从目前的工作频率300MHz和运算能力600M MAC(即每秒6亿次乘法—累加操作)提高到工作频率1GHz 和运算速度20亿MAC。完整的21535具有丰富的外围配置,包括USB和PCI接口,以及传统的DSP类的外设(图2)。产品系列中的下一代将针对特定的市场分区采用不同的外设配置。

如今一般的移动电话包含一个DSP和一个通用的处理器,如一个RISC处理器。这是因为有时在进行通用信号处理的同时还需要进行数字信号处理。例如,通过电话交谈时需要用到声音编码、压缩和其他DSP功能,同时用户可能还要按键盘上的按键,并阅读显示的信息。由于DSP必须实时运算以防止丢失采样点,因此对键盘和显示的控制必须由通用处理器来进行。

TI公司的一位董事兼高级DSP开发部经理Ray Simar说,“几年前,那些器件将是两块单独的芯片——通用的RISC处理器和DSP,”现在,我们可以把它们集成在同一个封装中。由于存储器是内置的,它们在功耗方面占有优势,面积也减小了。”

Simar接着说:“同时,电压也下降了。功耗大致与电压的平方成正比。如果你能始终降低电压的量值,就可以大大减少功耗。这很令人感兴趣,因为缩小装置的几何尺寸势必要求我们采用更低的电压,这与在DSP应用中降低功耗的需求相一致。”

在加快单个DSP—RISC处理器组合芯片研制进程的同时,TI和ARM最近宣布了一项协议:TI将获得许可,在ARM v6体系结构基础上开发IC。该结构体系是两个公司两年合作的结果,能使TI将其DSP与ARM的体系结构实现无缝连接。

ARM和TI两家公司这一为期两年的合作成果集成了双方技术的一些新的特征,改进了数据同步、共享存储管理并获得更有效的OS操作。其目标是提高最终系统在运行实时声频和视频程序时的性能,并保持低功耗。基于这种体系结构的产品将从ARM获得,形式是合作商经过许可后可以在所设计的ASIC或ASSP中使用相应的知识产权(IP)核。

StarCore公司开发的内核应用于Motorola和Agere System公司的标准产品,他们相信自己的解决办法适用于便携式应用,因为其核的应用效率(用低功耗和紧凑代码密度的组合定义)较高。与一些更为传统的DSP供应商不同,StarCore的研究小组只专注于核的开发,完成后将核移交给Motorola和Agere的设计队伍,来开发出标准的DSP产品。

为了在减小功耗的同时不至于降低性能,采用了传统的节能模式,如关闭未使用的那部分处理器。内核也可以在运行中改变其工作频率。

StarCore最新推出的SC140就是基于一个VLIW(超长指令字)类的结构。与前一代产品相比其改进之处在于:当指令调入执行单元时,无须使用OP指令。而且在分区指令方面没有对准的限制。这不会减少对存储器的读取操作,而执行单元在不使用时不必加以时钟控制。

SC140可以在0.9~1.5V的电压范围内工作,在0.9V工作时,核可以达到120MHz的频率。由于它是4MAC的结构,这就可以产生约480M MAC的计算速度(图3)。核在0.9V时的峰值功耗,包括对存储器的读取,一般在40mW以下(假定每个执行单元在执行一条指令,典型应用中并不总是这种情况)。

“对于一个典型的无线装置来说,我们希望它在尽可能接近1V的条件下工作,”StarCore公司一位市场总管Scott Beach说,“但对于一个高端系统,如3G系统来说,你可能要让它在1.5V下工作,才能使工作频率接近300MHz。”

StarCore体系结构的一个设计目标是确保兼容性,使得用户可以用C编译器开发大多数代码。“从编译的角度来看,关键在于编译人员要协助确定有多少个寄存器,并确保体系结构的各个不同的方面相互一致,从而保证编译器能利用这一点,并生成有用的代码。”Beach解释说,“我们的目标是让编译器开发并生成有用的代码,从而只需极少的手工优化工作。”

StarCore 新近宣布了一项与Wind River System公司的协议,为基于DSP的系统芯片(SoC)嵌入式应用建立一个集成的软、硬件开发平台。该平台将把Wind River的嵌入式软件和开发工具与最新的StarCore的DSP技术结合起来。根据该项协议,Agere、Motorola和Wind River将对Wind River的实时操作系统(RTOS)和用于StarCore体系结构的开发工具进行优化,以方便无线通信装置的开发。

Wind River将开发并提供一个C/C++编译器和一套运行分析软件、一个针对StarCore 的源程序级调试器和硬件调试工具,以协助早期的硬件和未来Tornado集成开发环境的研究。■(缪民译自《Portable Design》2001,9)

评论