FPGA电源系统设计能够采用并行工程吗?

在开发过程一开始时,如果设计人员就能够满足基于FPGA的设计对电源的要求和约束,这对于系统的最终实现而言是很大的竞争优势。但是,虽然技术文献在这方面进行了大量的介绍,目前基于FPGA的系统中是否有不实用或者很难实现的东西导致做不到这一点?尽管可以使用各种开发工具,例如特别针对FPGA工程的早期功耗估算器和功耗分析器等,电源设计人员最好能够在设计早期阶段,考虑电源系统的最差情况,而不是最佳情况,这是因为在硬件设计完成之后,测量功耗之前,动态负载需求还有很大的不确定性,会在静态低电流状态和全速工作状态之间波动。

本文引用地址:https://www.eepw.com.cn/article/271487.htm在当今的设计中,采用并行工程(CE)能否为使用FPGA器件的开发团队提供一种方法,在其工程中更方便快速的找到并提取出处理性能、材料表(BOM)成本和能效的最佳平衡点?了解并行工程怎样影响团队的设计投入,影响开发团队能否在FPGA工程一开始就满足电源设计要求,以及系统其它部分对电源的要求,这有助于回答这一问题(参考侧边栏目“并行工程”)。

并行工程这种机制支持设计团队更迅速的发现并解决一起工作的各学科之间所做假设的分歧问题,实现最终设计。任何设计团队都很难在设计一开始时就能够满足复杂系统的所有要求——结果,更有效的方法是,尽可能早的发现、识别并解决所做假设的分歧问题,做出设计决定,以尽可能低的成本,采用与工程所需产出最贴近的设计假设和决定替代以前的假设和决定。

设计后期的情况越来越复杂,最差情况下的FPGA电源系统设计能够采用并行工程实践吗?为回答这一问题,我们需要理解:是什么原因导致FPGA电源系统设计人员面临如此复杂而且不确定的设计,设计电源时,要做出哪些取舍?

复杂性和不确定性

设计团队中的每一名成员都体会到复杂性和不确定性——随着集成度的提高,以及设计的抽象化,复杂性和不确定性也稍有缓和,设计人员还能够接受和理解这种复杂性,并进行工作。设计即将结束时,每一学科都会对设计有所贡献,上游设计假设和决定会导致更加复杂和不确定,如果尽早进行协调和沟通,会减轻这方面的影响。

在越来越复杂的系统中,电源设计是下游学科之一。对于这一情形,让我们从电源设计人员的角度看一下复杂性和不确定性的来源。影响电源设计的两个关键FPGA规范是电压和电流要求。

FPGA电压要求越来越复杂,这是因为所需要的电源轨越来越多了。以前,内核和I/O单元需要两个电源轨,还有可能采用第三个用于其他功能,而现在的高端FPGA会需要数十个外部驱动的电源轨。

为什么所需要的电源轨数量会急剧增长? SRAM单元需要的电压要比内部逻辑门稍高一些,以保证可靠的全速工作,而待机模式的电压要低一些。工业标准会锁定各种I/O单元,以及不同电源的物理接收和发送接口,这些电源具有不同的供电噪声限制和电压电平,因此能够防止不同的I/O单元共享同一个电源轨,这增加了所需要的电源轨数量。例如,以太网运行的I/O电压与I2C总线不同。一个是板上总线,另一个是外部总线,但是都能够在FPGA中实现。降低敏感电路的抖动或者提高噪声余量会要求更多的电源轨,例如低噪声放大器、锁相环、收发器以及高精度模拟电路等,因为即使是工作在同样的电压下,它们也无法共享含有噪声分量的电源轨。

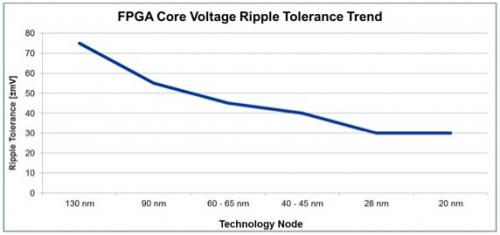

除了需要越来越多的电源轨之外,当今的FPGA工作电压要低于以前的产品代,这对于降低功耗和提高集成度很重要,但是由于电源必须维持要求越来越严格的电压容限,因此,这也提高了复杂度(参见图1)。例如,在28 nm技术节点,公开的FPGA内核电压波纹容限幅度比130 nm制造的FPGA低了一半多。误差余量百分比从5%降到3%,还会继续降到2%.满足电压容限要求有助于理解并满足FPGA电流要求。

图1.四个技术节点的平均电压波纹容限降低了一半多,这对于电源设计人员而言,意味着复杂度提高了。

fpga相关文章:fpga是什么

锁相环相关文章:锁相环原理 锁相放大器相关文章:锁相放大器原理

评论