FPGA研发之道(20)-片上系统

从最初的占地170平方的第一代ENIAC计算机开始,计算机开始了不断集成化、小型化的发展之旅。现今在单一芯片内部已经能够集处理器,存储,各型协处理器等,从而形成的强大的单芯片的片上系统(SOC),而这些片上系统已存在于生活的方方面面。因此FPGA内部支持片上系统,也算不上是新奇的事情了。ALTERA和XILINX已各自推出了各自应用片上系统(FPGA领域称之为SOPC,因此其片上系统可以根据业务需求来定义)。

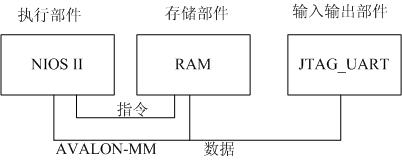

本文引用地址:https://www.eepw.com.cn/article/265803.htm只需几K的资源,就能实现一个SOC的最小系统,对于FPGA工程师来说,没什么比这个更有吸引力了。那么,作为一个片上系统来说,其最小系统应该包含哪些:其至少需要三个部件,执行部件(处理器),程序执行部件(内部存储器),输出部件(输入输出单元)。(其分别相当于PC上的CPU、内存条,键盘鼠标显示器)。下图所示在ALTERA的QSYS上实现NIOS的最小系统所需部件。

(1) 处理部件:NIOSII为ALTERA器件中所专有的软核处理器,而xilinx所对应的为microblaze的软核。通过在Qsys的界面工具中提供许多IP,而NIOSII也提供三个版本提供使用,分别是高速型,标准型,以及经济型。如果FPGA内部逻辑有限,可选择的经济型,其占用资源较少。如果需要内部资源丰富又需要运行嵌入式操作系统uclinux等复杂软件。则建议选择高速型,而要运行linux等操作系统,则在NIOSII高速型中配置MMU则是必须的。如无具体需求,则使用标准型即可。值得一提的是,NIOSII为哈佛型体系结构,即数据和指令分开,从Qsys可以看出,其接口分为指令接口和数据接口。

(2) 存储部件:对于在FPGA内部实现SOC来说,片内的块RAM就是实现SOC内部程序与数据的存储空间。也可以使用片外的存储区,如片外SRAM或者DDR等。也可以作为程序和数据的存储空间。对于NIOSII处理器来说,只有选取了片内存储区或者片外存储区,才能设定程序中断向量和复位起始位置的存储区。另外,虽然AVALON总线支持数据总线和地址总线通过片上互联同一接口访问单端口RAM。但建议使用时,例化为双AVALON接口的双端口RAM,一则是因为一般存储区所需RAM深度够大,一般支持真双端口RAM,另一方面,数据和指令分开,能够提升系统的性能。

(3) 输入输出部件:通常在嵌入式SOC系统中,最常用的输入输出部件就是串口(UART)。常常被应用于(打印printf(),scanf())函数的输入输出。如果系统设计了串口(一般为SOC系统中所必须的),则例化系统中的支持avalon接口的串口即可,如果系统中不幸没有,那么ALTERA公司提供了JTAG-UART接口提供给用户输入输出交互接口。即通过复用JTAG下载线来模拟串口的操作。如果系统中有多个输出输出设备,如有多个UART,则在编程时,需在BSP的环境中设定,选择使用哪个UART作为系统的输出。

使用ALTERA的Qsys工具可以方便的在FPGA上构建SOC系统。只需选择相应的IP(可以是系统自带,也可以使用自己构建支持avalon-mm接口的IP)。通过系统的互联从而构成一个片上系统。图形化的界面只需通过avalon总线连接信号将NIOSII和外设连接在一起即可。连接完毕后,还需要下面操作:

(1) 为每个外设设定地址,例如上图中RAM和JTAG-UART,每个外设都需要一个地址范围,可以点击系统中自动地址分配,也可以手动分配一个区间。只有为每个外设分配地址后(相当于整个系统的门牌号),处理器才能根据地址来访问各个外设。

(2) 如外设有中断,则为外设分配中断号,也可自动或者手动完成。如不分配中断的话,那么处理器访问外设,只有查询一种交互方式了。中断方式使用可以减少处理器的负载。

在ALTERA的QSYS工具中,硬件信息全部存储在sopcinfo。主要是包括各个外设的地址信息等,用于产生system.h。也就是说,作为软件和硬件的交互的渠道是每个外设的基地址,中断,和内部寄存器等信息。系统构建结束后,剩下的就可以软件编程了,运行在搭建的SOC系统上的第一个“hello world”的程序。

对于现在FPGA上的SOC设计,厂商为了其方便易用,做了大量的工作,只需按照其指南一步步,就可以实现相应的设计,但同时,也限制了对其基本原理的深入的理解。什么事情都有其两面性,作为FPGA工程师,SOC的原理则应该能够重点关注,这样不论是ALTERA还是XILINX其基本原理也是一致的。如不使用厂家的处理器核(NIOSII、microblaze),也可以使用其他的软核(如51等,ARM)在FPGA上实现SOC系统。只不过原来工具做的工作,就需要手动来完成了。

linux操作系统文章专题:linux操作系统详解(linux不再难懂)

fpga相关文章:fpga是什么

评论