约束设置与逻辑综合在SoC设计中的应用

摘 要: 介绍了约束设置与逻辑综合在SoC设计中的应用,并以一款SoC芯片ZSU32的设计为例,详细讨论了系统芯片的约束设置与逻辑综合策略。

系统芯片SoC是目前超大规模集成电路设计的发展趋势,其集成度高、功能复杂、时序要求严格。逻辑综合是SoC设计不可缺少的一环,它是将抽象的以硬件描述语言所构造的模型转化为具体的门级电路网表的过程。逻辑综合的质量直接影响芯片所能达到的性能,因而在综合过程中必须根据设计要求在时序、面积和功耗方面设置正确的约束。

本文针对中山大学ASIC设计中心自主开发的一款系统芯片ZSU32,以Synopsys公司的Design Compiler为综合工具,探索了对SoC芯片进行综合的设计流程和方法,特别对综合过程的时序约束进行了详细讨论,提出了有效的综合约束设置方案。

1 时序约束原理

同步电路是大多数集成电路系统的主流选择。同步电路具有工作特性简单、步调明确、抗干扰能力强等特点。但是,因为所有的时序元件受控于一个特定的时钟,所以数据的传播必须满足一定的约束以便能够保持与时钟信号步调一致。

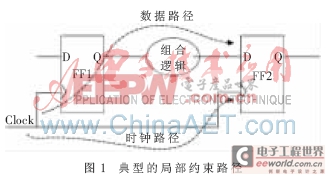

图1是一个典型的局部路径,它需要满足两方面的条件:防止数据太迟到达目的寄存器导致数据不能正确保存;防止新的数据过早到达导致覆盖了前一数据。

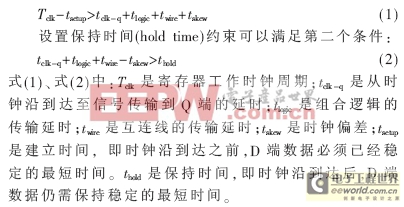

设置建立时间(setup time)约束可以满足第一个条件:

评论