从4004到core i7——处理器的进化史-CPU构成零件-4

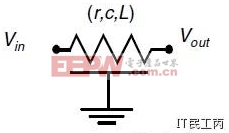

上一帖我们说到了IC的性能取决于R与C的乘积。看到留言后我发现还必须补充一个遗漏的事实:当器件的尺寸变得越来越小,连线在IC中越来越成为一个瓶颈。这是由于一个非常简单的原因:连线相对于器件的尺寸来说越来越长了。所以,EDA提供的placement&routing功能显得越来越重要。显然,你不可能手工布置几百万个cell的位置。在IC设计中,长的连线一般用下面的传输线模型来表示:

本文引用地址:https://www.eepw.com.cn/article/221763.htm

学过通信的同志一定对这个符号不陌生。解一个PDE之后,我们发现信号在传输线中是以波动的方式传播的。在这里我不讨论这个解的具体形式了。

顺带提一句,IC中的第一层,也就是最靠近硅表面的连线一般不是金属,而是多晶硅(poly-silicon)。

好了,在这个帖子中我将要介绍最后两个重要的概念:功耗以及比例缩小。作为第二章的结尾,在第5个帖子中,我们还会顺道看一看CMOS以外的一些设计模式。

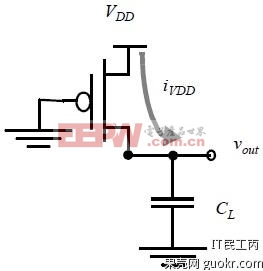

我们还是回到上一个帖子中的反相器上:

这张图上省去了一切多余的器件。PMOS管输入端接地表示这是一个非常理想的‘0’输入。

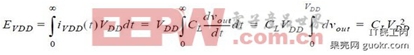

所谓功耗,就是指电路向直流电源索取的能量。

假设CL从0开始充电。我们可以算出:

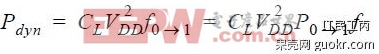

这个反相器的输入假如再从0->1,那么可以想象CL上的电荷在足够长的时间之后就会全部被泄放到地里面去了。当然,这个放电的过程仅仅是电容储能的释放,并不向直流电源索取能量。于是,我们很自然地想到:

其中P的下角标dyn代表的是dynamic。记得吗,CMOS电路在静态时是无功耗的!

于是我们可以知道,数字电路的功耗取决于频率、寄生参数、供电电压、翻转概率这四者。

而结合前面讲过的CPU超频的例子,我们知道为了保证正确性,频率一般要正比于供电电压。于是我们惊愕地看到:

功耗正比于频率的三次方!!!

评论