一种基于ARM内核SoC的FPGA 验证环境设计方法

引 言

随着片上系统(SoC) 设计的复杂度和性能要求的不断提高, 软硬件协同设计(Hardware/ Software Co2de2sign) 贯穿于SoC 设计的始终。软硬件协同设计是一个以性能和实现成本为尺度的循环优化过程,验证设计是其中必不可少的重要环节。目前大多数公司提供的开发验证系统(开发板) 存在两个弱点:一是开发板的性能、规模难以根据特定的设计需求灵活、自由地调节;二是开发板的功能大多数只能进行软件代码的调试,即使ARM公司提供的开发平台也只能调试部分硬件。这两个弱点均在一定程度上限制了软硬件划分的探索空间,使所设计的SoC 不能获得更佳结构实现的能力。

本文利用现场可编程门阵列(FPGA) 重用性好、现场灵活性好的优势,开发一个能进行详细的行为监测和分析的实时运行验证平台,实现软硬件的紧密和灵活耦合,从而克服上述结构的弱点,以全实时方式运行协同设计所产生的硬件代码和软件代码,构成一个可独立运行、可现场监测的验证平台。这样,不但能够提高SoC 流片成功率,加快SoC 的开发,而且可以降低整个SoC 应用系统的开发成本。

验证平台的设计

系统设计

图1 是我们设计的SoC 系统架构, 选用了ARM7TDMI 处理器核, 它是一个RISC 体系的32 位CPU ,具有功耗低、性价比高、代码密度高三大特色(ARM公司本身不生产芯片,普通用户无法获得ARM可综合的CPU 核) ,包括AMBA 总线、DMA 控制器和Bridge 、(外部存储器接口EMI) 、通用串行总线(USB) 客户端控制器、液晶显示器(LCD) 控制器、多媒体加速器(MMA) 、AC97 控制器、通用串口/ 红外(UART/ IrDA) 、通用定时器/ 脉宽调制器(TIMER/ PWM) 、中断控制器( INTC) 、同步外设接口(SPI) 、实时时钟(RTC/ WD) 、时钟和功耗管理单元(PMU) 。

图1 SoC的系统架构

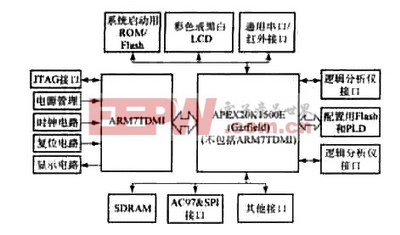

图2 是该SoC 验证平台的结构框图,选用Altera公司的APEX20K1500E 作为验证SoC 用的FPGA ,该器件由一系列的MegaLAB 结构构成,每个结构包含一组逻辑阵列块(LAB) 、一个嵌入式系统块( ESB) 及一个在MegaLAB 结构内提供信号通道的MegaLAB 互连。在MegaLAB 结构和I/ O 引脚间的信号布线通过Fast -Track 互连实现。另外,靠边的LAB 能被I/ O 引脚通过局部互连驱动。

该器件有如下特点:具有多核结构,支持可编程单芯片系统(SOPC) ,密度高,专为低电压应用设计,最多带4 个锁相环的时钟管理电路,多达8路全局时钟信号,每个I/ O 引脚具有独特的三态输出使能控制及可编程压摆率控制[1 ,2 ] 。使用该器件作为AMBA 总线模块、DMA 控制模块、EMI 模块、USB 模块及LCD 控制模块等多个IP 模块的硬件载体, 与ARM7 TDMI处理器构成了一个SoC的验证系统。

图2 中外围电路的主要功能是验证SoC 中各个接口IP 模块能否与ARM7TDMI 核、外部接口单元、硬件驱动软件和实时操作系统协调高效地工作。由于接口(如USB 接口、UART/ IrDA 接口、SPI 和LCD 接口等) 电路结构比较简单,且很多资料都有介绍,在设计时,除了注意通用的设计规则和印制电路板(PCB) 布局布线外,没有特别的要求(总结构框图中所有外围电路都在该开发验证系统中调试成功) ,同时,为了便于分析各个被验证的IP 模块在任意时刻的状态, 我们将APEX20K1500E 的大多数I/ O 引脚都引出到PCB 上,以方便SoC 开发人员使用逻辑分析仪进行信号实时采集和分析,也可让信号发生器产生一些特定信号通过以供系统调试使用。该开发系统在PCB 的设计时还特别注意了电磁干扰的屏蔽。

图2 验证平台结构框图

电路设计

电源的设计

拥有符合FPGA 要求的电压对该验证环境的设计十分重要。根据SoC 的发展趋势和APEX20K1500E增强型I/ O的特点,该平台选用2 . 5V内核电压和3. 3 V 的I/ O 电压,同时提供2. 5 V 和1. 8 V 可选电压,以满足SoC 更低电压、更低功耗的发展要求,方便以后重复使用。

评论