非易失性SRAM DS1747

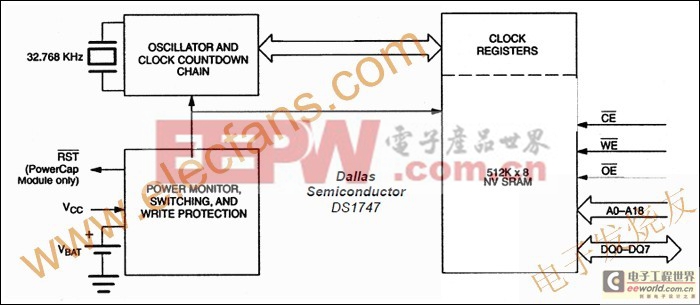

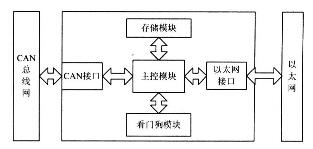

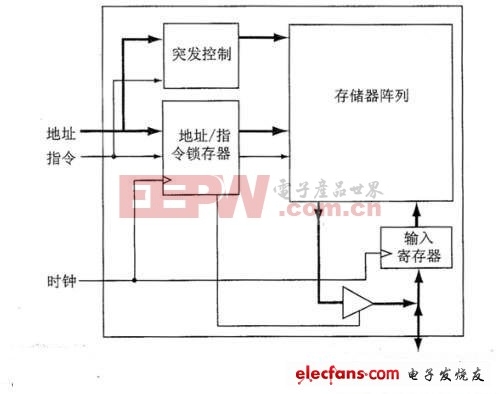

DS1747是功能完备、2000年兼容(Y2KC)的实时时钟/日历(RTC)和512k x 8非易失性SRAM。用户可通过如图1所示的单字节宽度的接口对DS1747内部的所有寄存器进行访问。RTC信息和控制位占用RAM中最高的8个地址。RTC寄存器包含世纪、年、月、日、星期、小时、分和秒数据,采用24小时BCD格式。器件可自动对每个月份及闰年进行日期校正。RTC时钟寄存器采用双缓冲,可避免在时钟更新周期内访问不正确的数据。双缓冲系统还可以防止访问时间寄存器时导致倒数计时无法减少而引起的时间丢失。DS1747还包含电源失效电路,用于当VCC电源超出容差时,禁止选通器件。由于低VCC引起不可预测的系统操作,该特性可以避免这种情况下的数据丢失,从而避免错误的访问和更新。

关键特性

集成的NV SRAM、实时时钟(RTC)、晶体、电源失效控制电路和锂电池

访问时钟寄存器方式与静态RAM完全相同,这些寄存器位于RAM中最高的8个地址

世纪字节寄存器;Y2K兼容

完全的非易失性,可在缺少电源的条件下工作10年以上

BCD编码的世纪、年、月、日、星期、小时、分和秒数据,可自动进行闰年补偿至2100年

电池电压指示标志

电源失效写保护,允许±10%的VCC电源容差

锂电池处于开路的保鲜模式,直至首次电源加电

仅对于DIP模块:

标准的JEDEC字节宽度512k x 8静态RAM引脚排列

仅对于PowerCap模板:

可表贴的封装直接与包含电池和晶体的PowerCap连接

可替换的电池(PowerCap)

上电复位输出

引脚兼容于其他密度的DS174xP时间保持RAM

可提供工作在工业级温度范围(-40°C至+85°C)的芯片

评论