用栅极驱动器集成电路制作的100W数字功率放大

由于加有负反馈,所以即使D类输出级所加的电源电压有所变动,对放大器的增益也影响不大。所以电源电路采用变压器电源,不对电源电压进行稳压。

为了在负载电阻8缴鲜涑?00W的功率,其电源电压应至少等于输出信号的最大振幅和D类输出级的电压损失之和。经计算可知输出信号的最大振幅为40V左右,所以电源电压至少应大于±40V。再考虑到输出级的电压损失和电源的负载特性,无负载时所需的电源电压至少应比上面的确良±40V电压高出20%,所以把无负载时的电源电压定为±50V。顺便说一句,输出级的电压损失包括大功率MOS-FET的导通电阻和输出端低通滤波器的电感的直流电阻(约50M剑┮?鸬牡缪菇怠8昧讲糠值牡缪菇翟?00W输出时约为0.7V[5×(0.09+0.05)]。

该电路的振荡频率由运算放大器构成的积分器和后面的开关电路的延迟时间及负反馈量来决定。积分器为二阶积分器,增大音频范围内的负反馈量可以改善放大器的失真率。

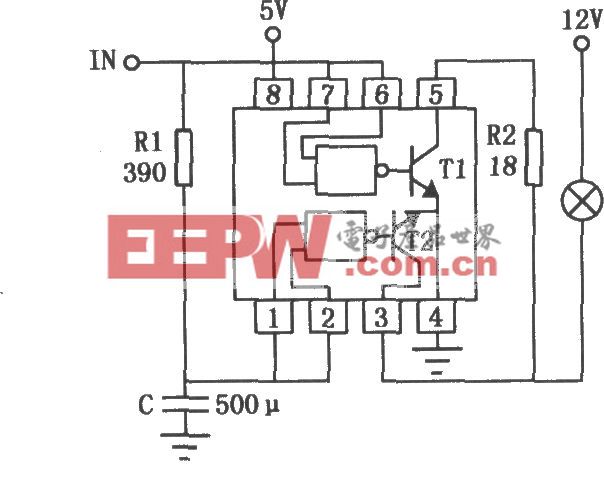

与运算放大器相连接的晶体三级管Tr1是电平移动电路。由于半桥驱动器集成电路IR2010是单电源供电的集成电路,需要将以地电位为基准的积分器输出向以负电源为基准进行电平移动。

将电平移动后的信号进入CMOS逻辑电路的反相器。用第一个反相器把信号变换成1此特的信号。为了向IR2010输入时间精度高(脉冲前、后沿陡峭)的PWM信号,用后面的多个反相器对脉冲波形进行整形。这样做还可以减小驱动器集成电路内逻辑延迟时间的不一致造成的影响。

驱动器集成电路的供电电压较高,由源电压会随开关状态产生变动,内部逻辑的阀值会产生变化,导致延迟时间不一致。当这种不一致过大时会引起大功率MOS-FET的开关定时不准确,空载时间变动,最终导致失真率变恶化。为了减小这种恶化,应加大驱动器集成电路的输入信号,并使输入信号的上升沿和下降沿尽量地陡。另外,驱动器集成电路的延迟时间是振荡所需的延迟时间的一部分。

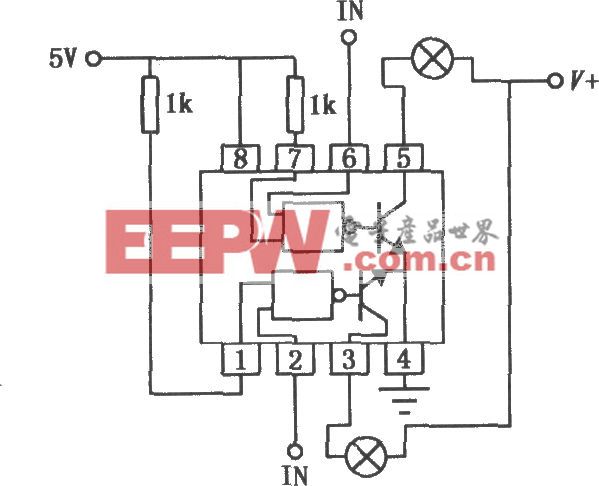

在IR2010的内部为了驱动后面的D类输出级的两只大功率MOS-FET,分别集成有两个驱动电路。上部驱动电路的电源是通过自举电路来提供的,图1中的C28(3.3礔)和D21即是自举电容和自举二极管。上部驱动电路部分与其他部分间的耐压达200V,是通过耐压200V的结来实现隔离的。

对IR2010来说,输出的驱动信号导通延迟时间比关断延迟时间长30nS左右,所以在驱动器集成电路的输入级可不必设置空载时间形成电路。为了实现低失真率,空载时间应短一些为好。但是当空载时间过短时,穿通电流将增大。

对于数字放大器来说,在过载时会反复出现周期短的峰值很大的浪涌电压。大功率MOS-FET的耐压至少应大于该浪涌电压和电源电压之和。经计算MOS-FET的最低耐压为130V,所以选用了耐压为150V的IRFB23N15D。该管的栅极总电荷量Qg≤56nC,导通电阻RDS(on)≤90m蕉己苄。?屎嫌糜谝?00kHz通断的数字功率放大器。

对于自激振荡型数字放大器来说如果不能确保在开关频率以上也能正常工作,其各种特性将会恶化。另外输入级的噪声特性对输出端的噪声电平的影响较大,所以运算放大了器要选用低噪声的运算放大器。在该放大器中选用了在高速和低噪声特性方面均比较优秀的LM6361。

采用表面安装的电容器有利于降低浪涌电压。输出低通滤波器采用了4阶LC滤波器。为了减小电感线圈的体积和直流电阻,又不出现失真,电感线圈采用了导磁率低的磁芯,在T-106的磁芯上用?.0的聚氯基甲酸酯线绕38圈。电感量为19.5礖。

C6和R15是由于一般的扬声器的阻抗在高频时会上升,所以特意接入的校正电路。

该机小信号电路和驱动器集成电路的电源用三端稳压器构成。D类输出级用的主电源(VDD和VSS)如果没有必要稳压的话,一般可采用变压器式的电源电路,这种方式比开关电源还省电。

图2是该机的频率特性,图3是该机的失真率特性。就其特性而言还不能与模拟放大器相比,但数字放大器是发展方向,总有一天数字放大器会成为音频放大器的主流。

评论