基于固态存储器的ECC算法分析及实现

评价存储器的一个重要指标就是它的可靠性,在一般的数据存储中,几个位的错误可能不是很关键的问题,如果但是发生在某个敏感的数据上,这个小小的故障可能会导致严重的后果。因此,必须采取一些措施来及时检出并纠正出错的数据。目前常用的方法有:奇偶校验、CRC校验、重复码校验等。

ECC校验是在奇偶校验的基础上发展而来的,它将数据块看作一个矩阵,利用矩阵的行、列奇偶信息生成ECC校验码。它能够检测并纠正单比特错误和检测双比特错误,但对双比特以上的错误不能保证检测。它克服了传统奇偶校验只能检出奇数位出错、校验码冗长、不能纠错的局限性。文中在高速大容量固态存储器的硬件结构基础上,详细介绍了ECC校验码的生成规则以及ECC校验流程,并用C语言和VHDL语言两种方法实现了该算法。

1 存储器的硬件结构及芯片介绍

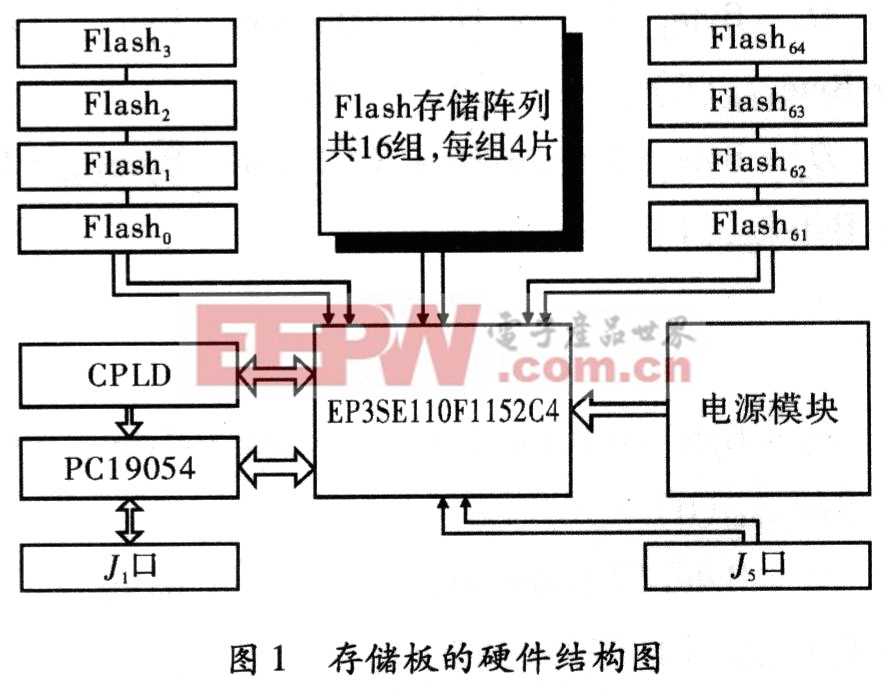

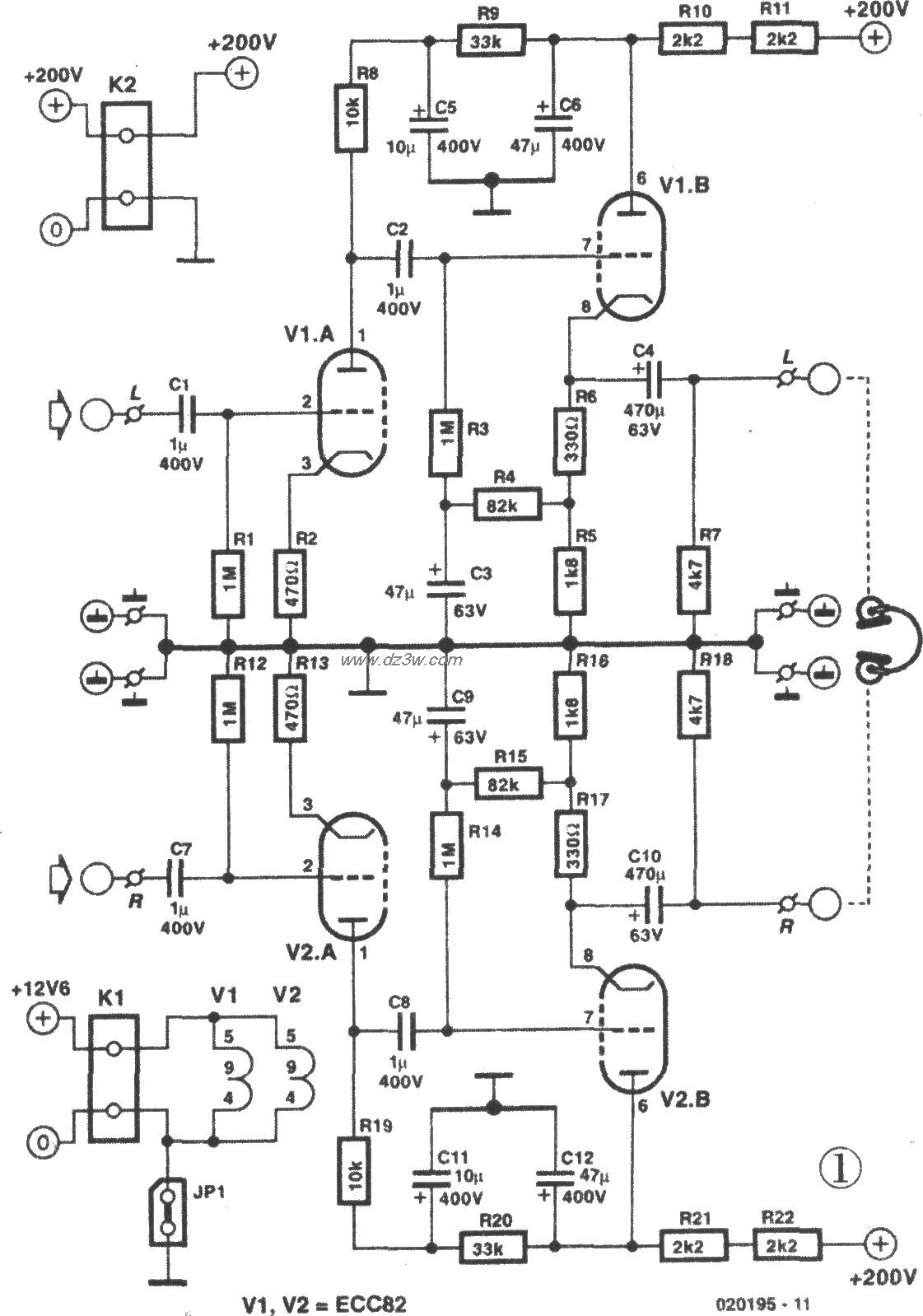

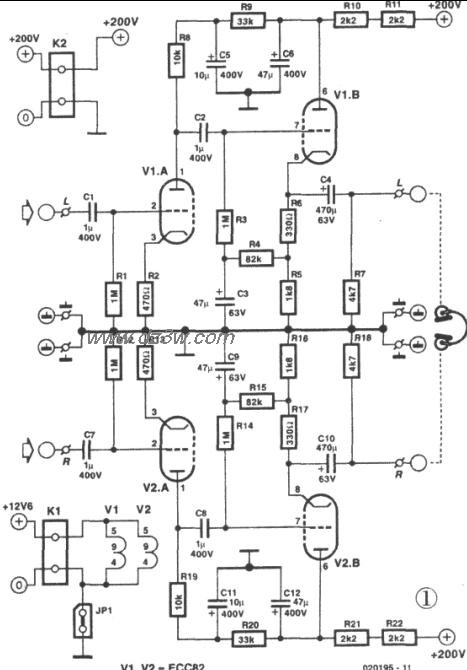

本存储器是以FPGA为控制核心,用64片Flash芯片构成存储阵列,采用CPCI接口实现数据的高速率存储。Flash存储阵列分为16组,每组4片,每组Flash芯片共用数据和控制总线。该存储器的硬件结构图,如图1所示。

存储板上的存储芯片用的是Samsung公司的高速大容量固态存储芯片K9W8G08U1 M Nand Flash Memory,其容量为1 G×8 bit,分为8 192个块,每个块又分为64页,1页有(2 k+64)Byte,其中一页有64 bit的空闲区。存储板上的控制芯片是Ahera公司的高端FPGA芯片EP3SE110F1152C4,它负责数据的缓冲和整个存储器的时序控制,并负责以页为单位生成校验码,并把校验码存人到页的空闲区内。下面以1页2 048 bit为单位介绍校验码的生成以及校验流程。

2 EGG算法分析及校验流程

2.1 EGG校验码生成规则

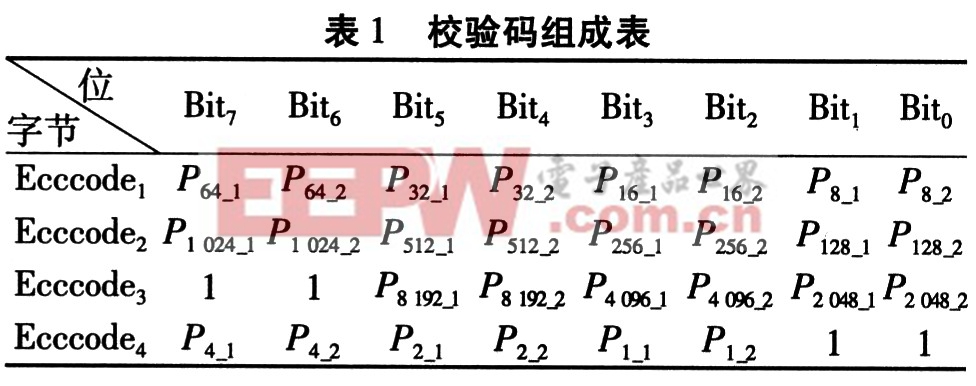

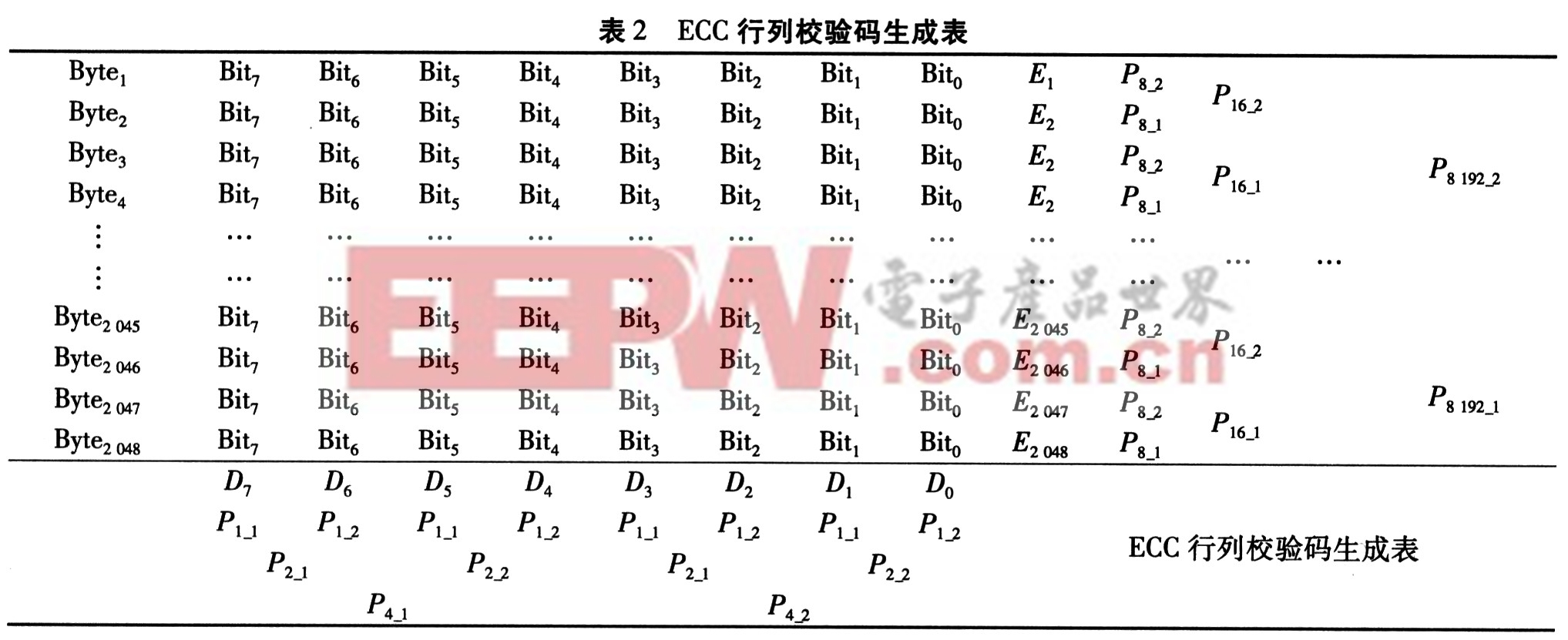

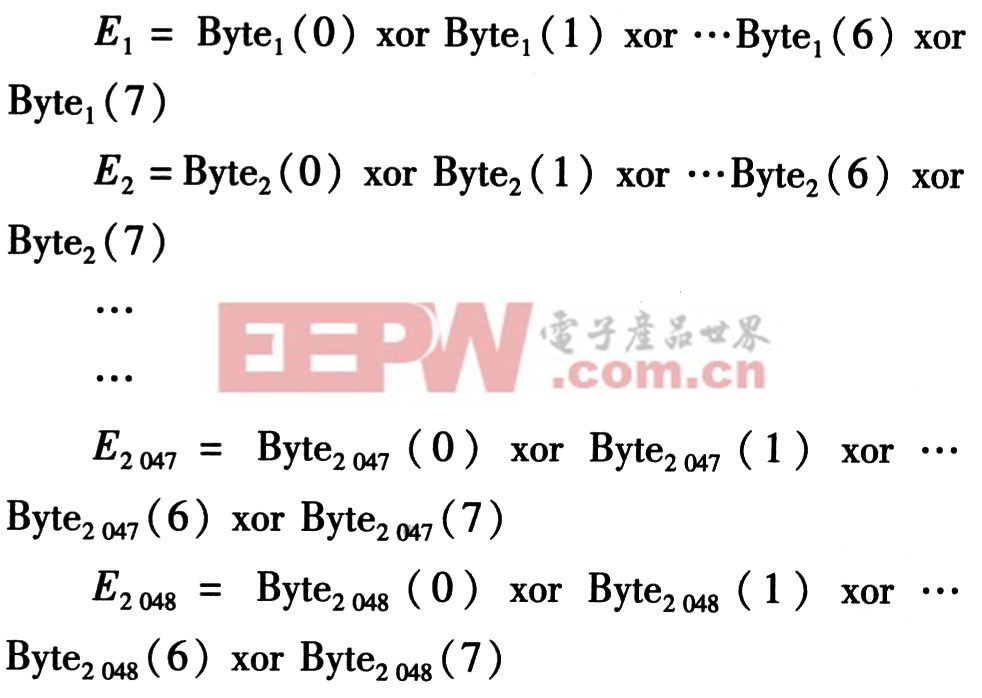

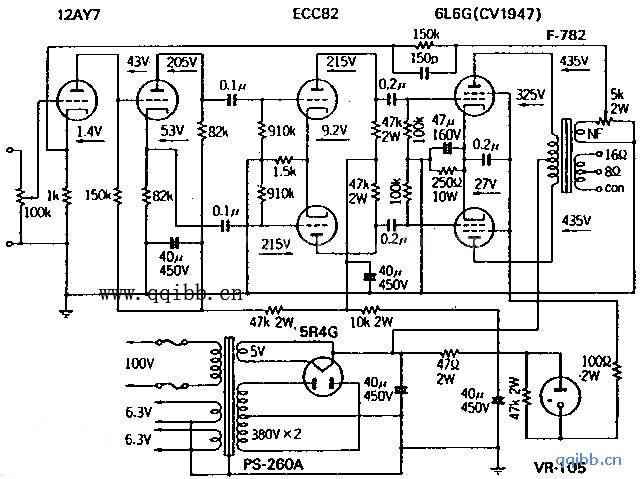

Flash在读写数据的时候是以页为单位进行的,一页有2 048个数据,所以可以以2 048 bit为单位生成校验码。每个数据有8位信息组成,可以把这2 048个数据看成2 048×8的矩阵,这样就可以分别生成行校验码和列校验码来分别校验。ECC校验中,每2 048个数据生成4个字节的校验码,这32位的校验码分成3个部分:6位的列校验信息,22位的行校验信息,其余的4位置1,ECC校验码组成,如表1所示。

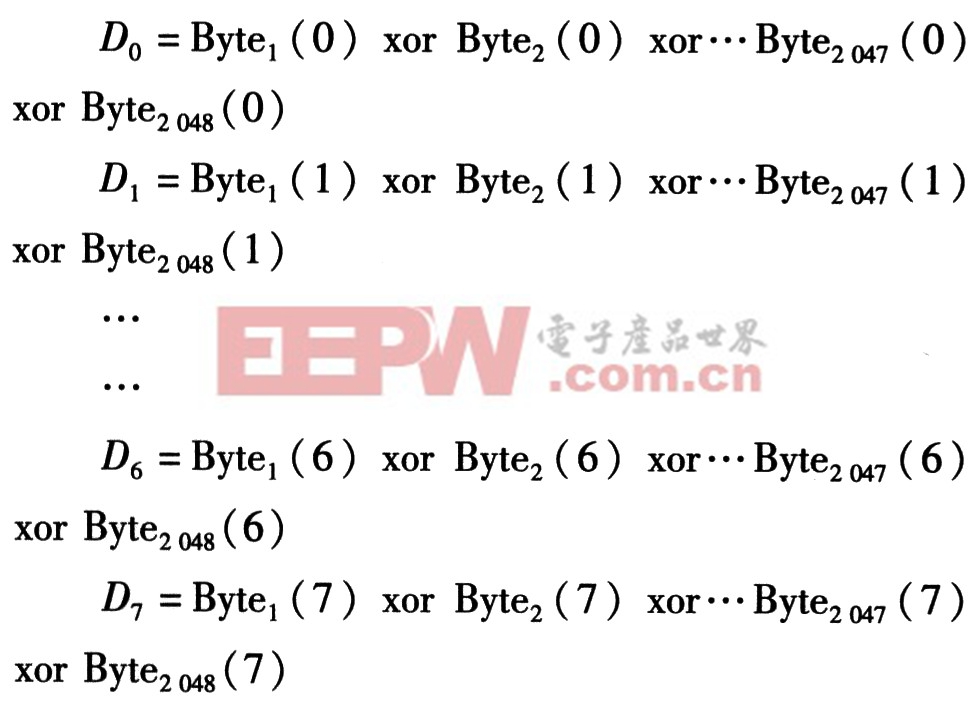

其中P4_l,P4_2,P2_1,P2_2,P1_1,P1_2是列校验码,而P8_1,P8_2,P16_1,P16_2,P32_1,P32_2,P64_1,P64_2,P128_1,P128_2,P256_1,P256_2, P512_1,P512_2,P1024_1,P1 024_2, P2 048_1, P2 048_2, P4 096_1,P4096_2,P8192_1,P8192_2是行校验码。行列校验码生成表,如表2所示。

评论