- 降低任何嵌入式设计的体积和成本的常用方法是使用具有较少I/O引脚的通信总线。虽然从并行总线发展到串行总线可明显减小体积和降低成本,但是从一种串行总线发展为另一种具有较少引脚的串行总线也很有用。用串行总,降低任何嵌入式设计的体积和成本的常用方法是使用具有较少I/O引脚的通信总线。虽然从并行总线发展到串行总线可明显减小体积和降低成本,但是从一种串行总线发展为另一种具有较少引脚的串行总线也很有用。用串行总线替

- 关键字:

串行总线 体积 引脚 并行总线

- [导读] 由于FPGA技术和ARM技术应用越来越广泛,通过设计并行总线接口来实现两者之间的数据交换,可以较容易地解 ...

- 关键字:

ARM 并行总线 机载雷达

- 摘要:通过EP2C20Q240 器件和LPC2478 处理器,研究ARM 应用系统外部并行总线的工作原理和时序特性,以及在FPGA 中 ...

- 关键字:

FPGA ARM 并行总线

- 0 引言在数字系统的设计中,FPGA+ARM 的系统架构得到了越来越广泛的应用,FPGA 主要实现高速数据的处理;ARM 主要实现系统的流程控制.人机交互.外部通信以及FPGA 控制等功能.I2C.SPI 等串行总线接口只能实现FPGA 和AR

- 关键字:

FPGA ARM 并行总线 仿真

- 引 言

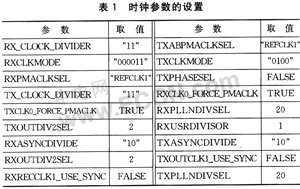

目前,多数计算机、嵌入式处理设备和通信设备都采用并行总线,但随着芯片性能不断提升和系统越来越复杂,数据传输带宽已成为提高系统性能的瓶颈。虽然增大并行总线宽度可以提高芯片与芯片之间、背板与背板之间的数据吞吐量,但是数据线的增多和传输速率的加快会使PCB布线的难度提高,并且增加了信号延时和时钟相位偏移。高速串行互连技术成为提高数据传输带宽的有效解决途径。

新的串行总线技术不断涌现,如新推出的串行总线标准有PCI-express、RapidI()、10Gigabit Etherne

- 关键字:

嵌入式 RocketIO 通信 并行总线 串行总线

并行总线介绍

您好,目前还没有人创建词条并行总线!

欢迎您创建该词条,阐述对并行总线的理解,并与今后在此搜索并行总线的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473