Chiplet 潮流中,谁是赢家?

大型芯片制造商专注于小芯片,将其视为将更多功能集成到电子设备中的最佳途径。现在的挑战是如何拉动芯片行业的其他部分,为第三方小芯片创建一个市场,可以使用特定标准从菜单中进行选择,这些标准可以加快上市时间,帮助控制成本,并像内部开发的芯片一样可靠。

本文引用地址:http://www.eepw.com.cn/article/202401/454515.htm到目前为止,第三方小芯片使用一直断断续续。普遍的共识是,第三方小芯片市场将在某个时候蓬勃发展,部分原因是购买小芯片比构建它们更便宜,前提是有足够的互操作性标准。最大的未知数是,与内部开发的小芯片相比,这些小芯片的性能如何,这反过来又会影响采用的速度、可用的市场机会总量以及随后的市场整合速度。

这是由于几个变量造成的。一方面,据估计,所有新启动的芯片设计中有 30% 至 35% 供大型系统公司内部使用。因此,这些公司不是使用现成的处理器和 IP,而是从头开始设计系统来优化其内部流程或数据类型。为这些应用开发的一些小芯片是高度专业化且具有竞争力的秘密武器,但这些系统中还有许多其他功能可以由第三方小芯片开发商开发。

另一方面,小型联盟正在围绕不同领域形成,例如生物或汽车应用。其中一些涉及代工厂和 OSAT,它们开始为本质上是装配设计套件制定标准,而另一些则正在有机开发。但在所有情况下,重点都是基于小芯片设计的大规模生产,并具有可预测的产量。

此外,与必须符合特定工艺技术的软 IP 不同,小芯片可以在任何工艺节点上开发。它们是否可以从一家晶圆厂互换到另一家晶圆厂还有待观察。然而,混合和匹配流程节点的能力为更多选择打开了大门。例如,开发人员可以在任何工作效果最好的节点上创建完全模拟的小芯片,而不是最先进节点的平面 SoC 所需的大部分数字芯片和一些模拟芯片。这开辟了一个基于 PPAC 的全新潜在市场。

小芯片代表了自摩尔定律诞生以来最根本的转变之一。这个想法已经存在了数十年,但在 finFET 推出之前,平面微缩的好处始终超过了改造供应链、设计和制造工艺、更新或添加新设备以及因故障而造成的中断所带来的巨大挑战。所有这些仍然是一个巨大的挑战,也是难以预测变化速度的主要原因之一。

AMD、英特尔和 Marvell 等大型芯片制造商已经证明小芯片的有效性,并且他们正在从其开创性工作中获益。但如果历史可以说明事情将如何演变,那么这些公司自己开发所有本质上硬化的知识产权在经济上并不有利。这是他们支持新的互操作性标准(尤其是 UCIe)并推广商业市场理念的原因之一。此外,各个政府机构还制定了利用现成的商用小芯片,作为加快上市时间并最终降低成本的一种方式的目标。

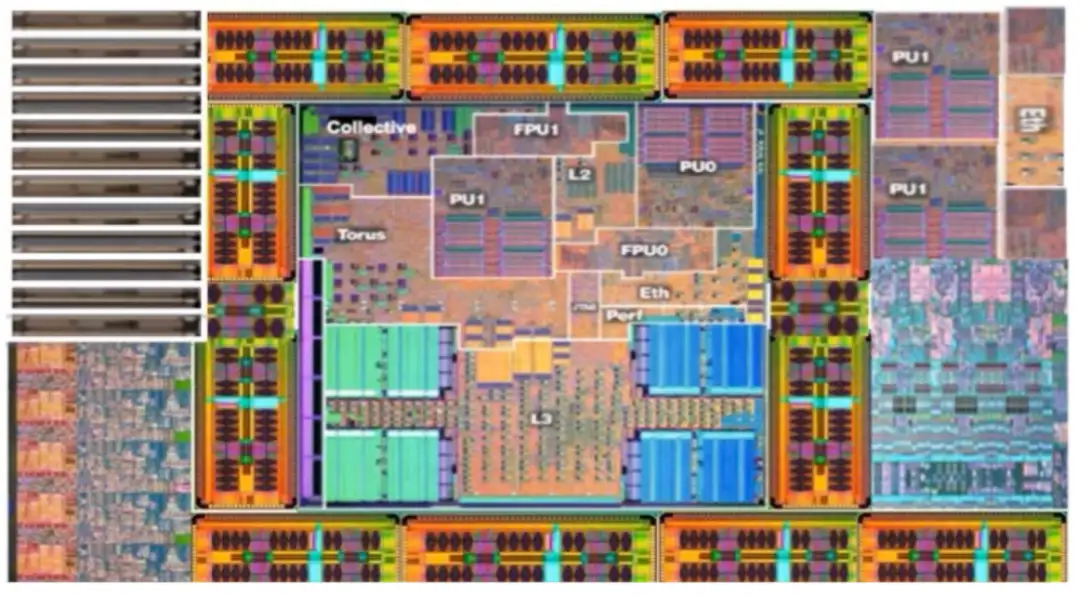

图 1:NIST 的小芯片架构。来源:美国国家标准技术研究所

尽管如此,正如这些初始实现所证明的那样,集成小芯片和组装它们比听起来要困难得多。大型芯片制造商通过构建小芯片的底盘来实现这一目标。这允许在特定参数内设计小芯片,例如面积、噪声(电磁、功率、基板等)、互连位置、材料相互作用和许多其他特性。但他们也使用一组对他们的设计很重要的狭窄参数来解决问题。

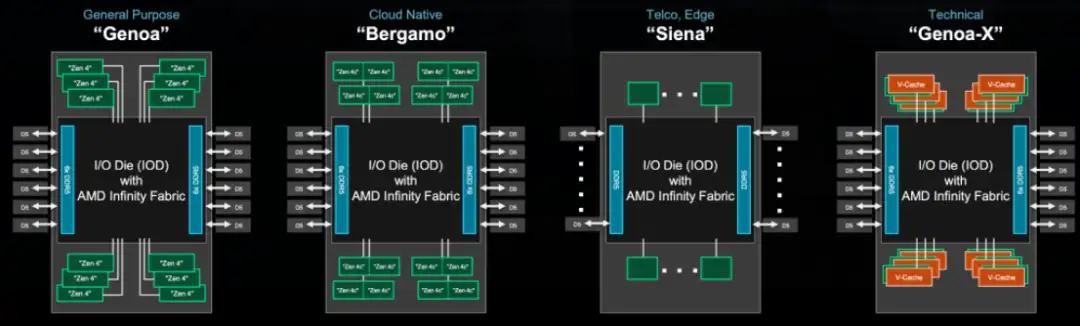

图 2:AMD 的 EPYC Gen 4 处理器使用小芯片来实现不同应用的可扩展性。来源:AMD/2023 年热门芯片

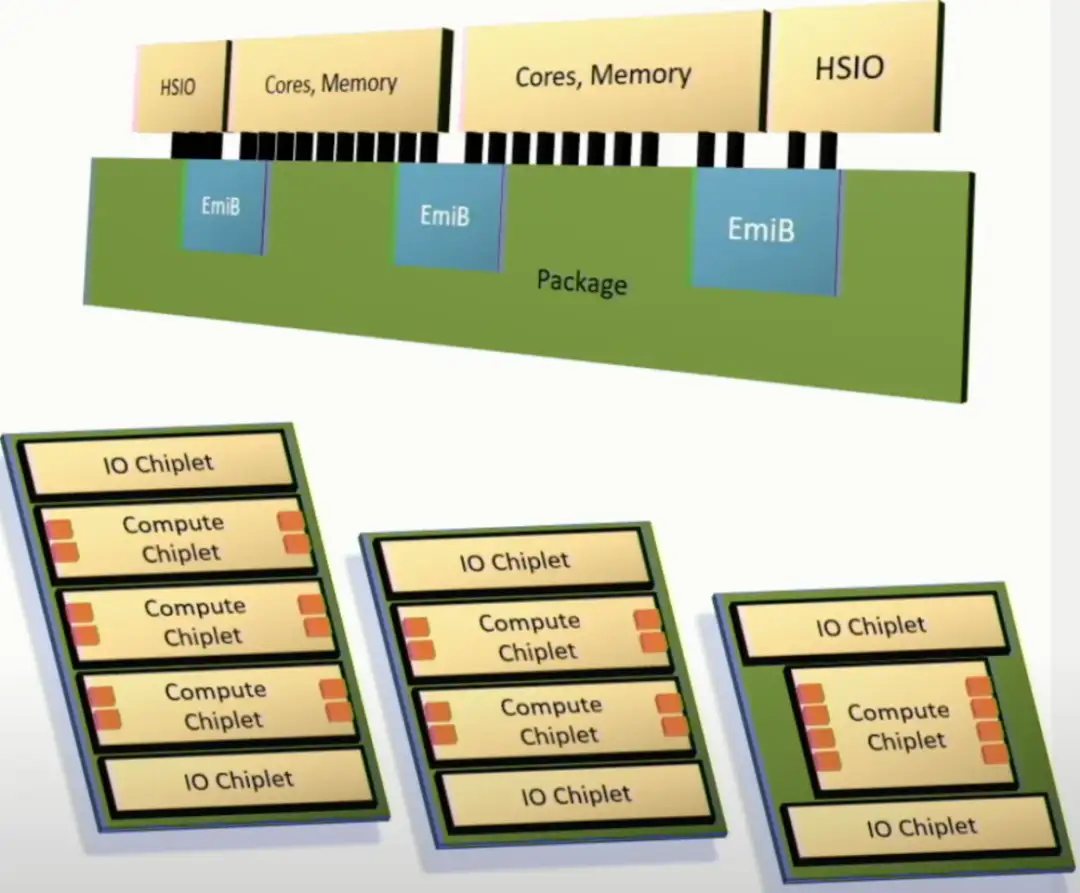

图 3:英特尔基于计算小芯片及其多芯片互连桥 (EMIB) 的可扩展至强架构。来源:英特尔/Hot Chips 2023

英特尔的小芯片方法类似。Advantest America 负责美国应用研究和技术的副总裁 Ira Leventhal 表示:「即使你有一套能够很好地协同工作的小芯片指南,你仍然会遇到各种工艺变化、封装变化等等。您可以提供芯片匹配和支持左移等功能,以便更快地发现缺陷,这样就不会产生大量的包装成本和废料。但在这个更复杂的环境中,如何优化产量?这确实很重要,即使您有一组可以一起发挥作用的最佳事物。需要在各个步骤中采取更多措施才能完成这一任务。」

小芯片还被高度针对性地用于其他设计,由 OSAT 将它们集成到先进的封装中。在这种情况下,它们就像 加密 IP 一样使用,而不是作为基于芯片的设计的一部分。

「我们看到我们的客户使用小芯片进行高性能计算以及网络交换机,」日月光高级工程总监欧力在最近的 CHIPCon 小组会议上表示。「他们关心性能和信号完整性。例如,您可以使用光纤 I/O 来替代高速 SerDes。因此,现在小芯片正在多个市场和多种应用中使用,并且未来的采用率将会越来越高。」

对于商业市场,关于小芯片如何准确表征的标准仍在制定中。尽管如此,这种方法还是有一些明显的优点。由于小芯片比光罩尺寸的 SoC 更小,因此良率通常更高。真正的集成挑战来自小芯片的外部。还存在一些挑战,包括如何在组装后单独测试和检查它们,以及如何测量芯片移位等内容。例如,特定用例的动态功率密度可能会因电阻和静态漏电流而增加热量。这反过来会导致翘曲,从而对将小芯片固定到位的键产生压力。处理所有这些问题需要新的流程来在设计周期的早期解决这些问题,以及新的设备和全新的工艺步骤。

Chiplet 的优势

使用 Chiplet 有三个主要原因。

首先,无论工艺节点如何,它们都可以混合和匹配,这显著降低了开发半导体器件的成本。「随着这些特定领域的架构越来越专业化,如果它真正推动我们为每种架构采用差异化技术,它有可能对晶圆厂、设备制造商和生态系统的其他部分产生巨大的颠覆性,」他说。Lam Research 计算产品公司副总裁 David Fried 在 SEMI 最近举行的关于计算未来的小组讨论中发言。「如果你回顾 15 到 20 年前,当单片集成节点一个接一个地缓慢前进时,我们将异构集成所需的一些流程创新视为附加的。但现在,如果你看看到达下一个节点的成本,特别是单片集成的成本,那么突然之间这些异构集成过程似乎真的很便宜。」

其次,小芯片可以换入或换出设计,以针对特定领域和应用进行定制。这使得芯片制造商能够创建高度针对特定应用的设计,为更特定的领域和用例定制类似的芯片,无需从头开始重新创建所有内容即可更新它们,并添加比单个芯片上可用的更多功能。

英特尔硅架构工程师 Swadesh Choudhary 表示:「当我们期待拥有不同的技术节点时,我们可以将它们混合搭配在一起,并将一些模拟内容保留在比最新技术更稳定的技术中。您可以将不同的加速器与相同的计算引擎集成,并可能通过针对不同应用程序的定制包加快上市时间。通过封装中的小芯片,您可以更轻松地做到这一点。」

小芯片的第三个主要好处是,即使是首次设计,它们也可以显著加快上市时间,从而使芯片制造商能够更快地进入市场。

「归根结底,问题在于 PPA 和上市时间,」Amkor Technology 的小芯片/FCBGA 集成副总裁 Mike Kelly 说道。「这从高端开始。数据中心的人员首先推动了它,也许也是最困难的。但它正在渗透到我们今天看到的每一个计算机类中,数据中心、个人电脑市场和手机市场。汽车正变得计算密集型,并面临着与其他汽车相同的限制。现代节点价格昂贵,晶圆成本也很高。你可以通过突破真正高性能的部件来管理它。这是一条很长的 S 曲线但它肯定是在向新的地方过渡。」

并且有充分的理由。Synopsys 首席战略官 Antonio Varas 在 SEMI 活动上指出,目前只有约 35% 的芯片设计项目按计划进行,约 25% 的项目在首次硅片上就取得了成功。与此同时,需求每年以 9% 至 11% 的速度增长,而供应量则以 7% 至 9% 的速度增长。到 2030 年,需求预计将增长 17%,这主要是因为半导体被用于各种新市场和新应用。

挑战

这就是小芯片发挥作用的地方,要使这一切顺利进行,需要在各个层面制定标准——而这只是一个开始。

「你肯定需要标准,」台积电现场技术解决方案副总裁 Paul Rousseau 说。「这就是 3DFabric 和 3Dblox 背后的整个理念,并且有多个层次。其中一个级别是 EDA 端或 I/O,UCIe 正在成为芯片间通信的标准。除非有巨大的好处,否则为什么要使用不同类型的 I/O?另一件事是在硅本身或封装上。挑战之一是每个人都有一个奇特的想法。这需要大量的开发时间才能证明。因此,我们正在努力让人们采用标准解决方案。这就是我们对硅所做的事情。我们有设计规则和模型,我们知道会起作用。封装也有同样的目标。这并不是每次都重新发明轮子。」

最初,这意味着商用小芯片的选择更加有限。但这是否意味着不太优化的设计更难确定,因为将 SoC 分解为不同的强化功能可以让设计团队更轻松地确定这些功能的优先级并划分设计。如果有标准来规定不同的芯片如何组合在一起以及如何测试它们,那么随着时间的推移,它们可能会比一次性的设计更加可靠。

芯片设计的重大变化之一是关注数据如何在芯片中移动,随着需要处理的数据量持续增长,这一点非常重要。这引发了一系列变化,例如新材料和不同的设备组装方式。混合键合是人们高度关注的领域之一。由于需要比标准互连更快地传输视频和大型图像,这种技术首先在图像传感器中实现。例如,UMC 于 2023 年 2 月与 Cadence 签署了一项协议,提供一个可以加速这一过程的平台,特别是对于成熟节点,这是许多小芯片将被开发的地方。

举例来说,目前最快的一些计算机使用的组件,如商用的 ARM 内核。关键在于数据路径和与内存的物理连接、软硬件协同设计以及人工智能/机器学习的稀疏算法。随着计算变得更加分散,例如汽车和便携式设备与智能城市基础设施进行通信,真正的价值可能不再在于谁创造了最快的处理器,而更多地在于无缝连接。

更大的挑战可能在业务方面。「问题是这是否会转化为商业小芯片市场,您可以从第三方以低廉的价格采购它并将其集成到您的设计中,」Varas 说。「您需要的不仅仅是标准接口。这里有一个商业模式的问题。如何鉴定小芯片的资格?你如何测试它们?所以标准接口将会出现。但第二部分并不像 IP 模型的演变那么简单。情况要复杂得多。这项技术可能是可行的,但它还包括商业模式、供应链协调等等。」

此外,商业小芯片还存在数据共享的问题。大型芯片制造商的一大优势是能够在公司内部共享数据,以便可以针对最终应用或用例优化小芯片。不同公司之间交换数据要困难得多,因为公司非常担心数据泄露或被盗。

「有数据安全,也有数据共享,」林氏集团的弗里德说。「这些并不相互排斥,人们必须消化这一点。我们开始打破使用云来完成我们害怕使用云的事情的障碍。我们正在努力解决的是数据共享以获得更高的价值。飞机就是一个例子。这些飞机的所有者与飞机发动机制造商共享数字孪生和数字线程的维护记录和数据,并且他们可以对故障进行建模并进行预测性维护。航空航天行业的一些公司正在与所有这些不同的公司共享其产品的私密数据,这对所有这些公司都有好处。这种情况在我们的行业中并没有发生太多。这种情况发生在银行业,就像当你刷信用卡时,它会立即检查是否存在欺诈行为。这些模型建立在来自多个不同银行的数据之上,并且全部联合在一起。这就是我们作为一个行业失败的地方,因为我们在整个生态系统的数据共享方面落后于银行业和航空航天业 10 年。」

系统与芯片

设计方面还存在其他挑战。将小芯片集成到封装中使设计问题远远超出了单个芯片的范围。现在它是需要协同工作的芯片的集合,并且不再由单个团队在一个地点开发。

「我们已经从设计芯片转向设计系统,」Synopsys 的 Varas 说道。「我们正在处理三个主要问题。我们有新的复杂性向量,这需要系统设计的并行化。而且我们还缺乏人才。如今,60% 的 EDA 用户是经典半导体公司。另外 40% 是超大规模企业、初创公司以及 ASIC 或 IP 供应商。2019 年至 2022 年间,先进芯片的设计启动数量增加了 44%,但不断扩大的生态系统也加剧了碎片化。有更多的选择和复杂性,这增加了设计的破坏性。」

日月光公司的李对此表示同意。「设计师需要采取与过去不同的做法,过去以 PCB 为中心,使用 GUI 为主的设计工具,」她说。「他们不需要设计扇出或有源中介层。因此,旧的封装设计人员现在必须管理 LVS(布局与原理图)、CRV(约束随机验证)测试的 IC 级工具,并可能运行一些 SIPO(串行输入/并行输出)分析。我们需要与客户拥有相同的波长。此外,封装变得越来越大,为了控制翘曲,需要材料和工艺技术的创新。我们需要拥有已知良好的芯片、已知良好的模块,并且我们需要进行多次测试插入以确保每个过程都良好并且能够产出。最后,组件级测试将不再通过,这就是我们采用和实施系统级测试的原因。」

结论

Chiplet 在某个时候将会变得普遍。根本没有足够的体积来支持缩小芯片上所有部件的成本,最终公司将专注于他们最擅长的事情,并让其他人开发对竞争力或差异化没有贡献的组件他们的产品。

主要问题(至少在最初)与寻找将小芯片集成到设备中的标准方法有关,确保它们随着时间的推移按预期工作,以及如何共享数据以便行业能够快速发展。其中包括业务和技术问题,而且数量很多。尽管大型芯片制造商基本上都在单干,但随着成本受到严格审查,以及竞争为一些零部件创造了公平的竞争环境,这种情况将发生变化。但所有这些因素变化的速度有多快,以及是什么提供了竞争优势,将因市场、公司以及整个行业突然出现的技术、商业和地缘政治的新发展而有所不同。

Chiplet 的方向是明确的,有足够的力量在推动它。但在短期内,甚至可能更长时间内,时机、独特的挑战和生态系统合作仍将更加难以应对。

评论