新型态竞争风云起 EDA启动AI芯片新战场

AI将引导全世界走向工业革命以来,最大幅度的社会经济革新。

本文引用地址:https://www.eepw.com.cn/article/202006/413939.htm相关厂商必须快速将运算芯片上市,来处理AI架构的全新挑战。

这样的需求正驱使EDA工具日新月异,便于开发更高等级的方案。

随着AI技术的逐渐扩大应用,复杂性也不断增加,人们越来越清楚地知道,AI及其许多工具(例如深度学习、机器学习等)都将再一次引导全世界走向工业革命以来,最大幅度的社会经济革新。

尽管AI的使用,在道德层面上仍然存在着许多的争议,但不可否认的是,尽管目前仍只是处于AI发展的初期,然而AI已被大量部署于许多不同的领域,用于改善并实现机器的自动化。从数据的收集、通讯、机械人技术、工厂自动化、汽车设计到IC设计产业,都可以见到AI的踪影。特别是在IC设计的EDA领域,AI的应用案例更是不胜枚举。

AI迈入自主系统时代

根据Mentor Graphics(明导国际)所发表的白皮书指出,正由于得益于最新的技术进展,AI现已进入自主系统的时代,让人们可以拥有强大的能力,来处理运算密集的复杂任务。AI系统既便利又强大,可以用来解决全球面临的各种重大挑战。

AI系统包括三部分,超大数据集、数据处理算法,以及用来处理数据的运算硬件。一般来说,AI系统必须要能够快速地处理大量数据,才能实际发挥作用,而这就需要使用快速的运算能力。AI对于运算能力的需求,也催生了AI芯片(或者AI加速器)这个快速成长且充满竞争的新市场。要在这个市场上领先群雄,就必须快速将芯片上市,并且透过设计与测试的解决方案,来处理AI芯片架构的全新挑战。

提高AI运算效能

从Mentor Graphics的研究数据中可以发现,AI竞赛的展开,使得AI运算的需求大增,每3.5个月便增加一倍,自2012年起至今,已经增加了300,000倍。接着来看这三家处理器厂商的案例,他们各自采用了不同的硬件技术,来满足AI运算市场的成长需求。Graphcore与Mythic这两家新创公司是以ASIC芯片的方式提供AI运算能力,其ASIC架构是以创新的大规模平行架构为基础,能够大幅提升AI系统的数据处理能力。至于Intel、AMD与Nvidia等处理器大厂,则是持续开发并优化现有的处理器架构,包括GPU、CPU以及FPGA等,使其能满足AI系统的运算需求。

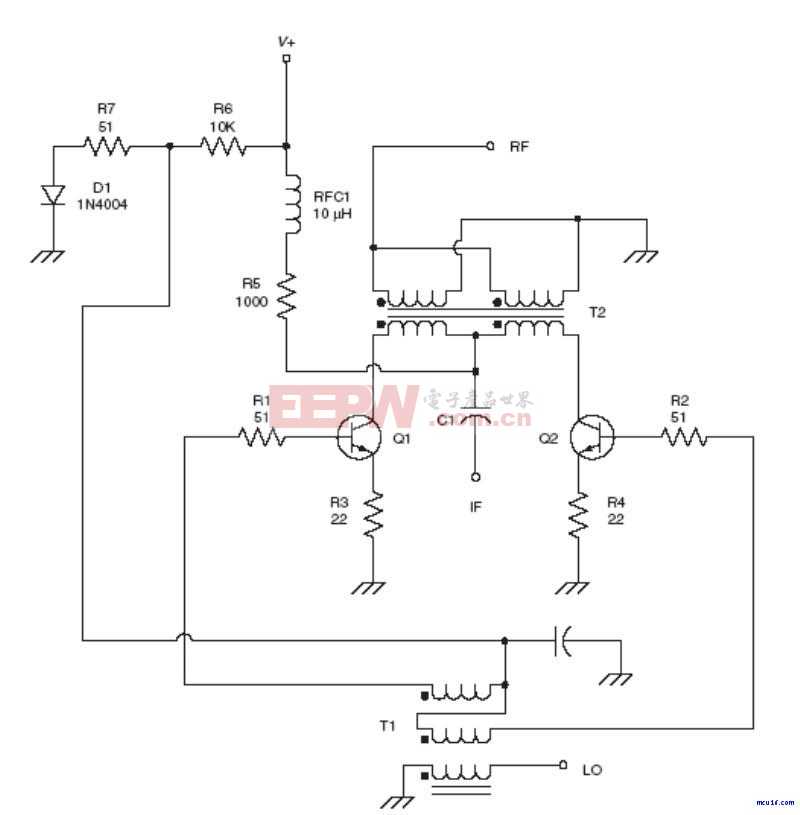

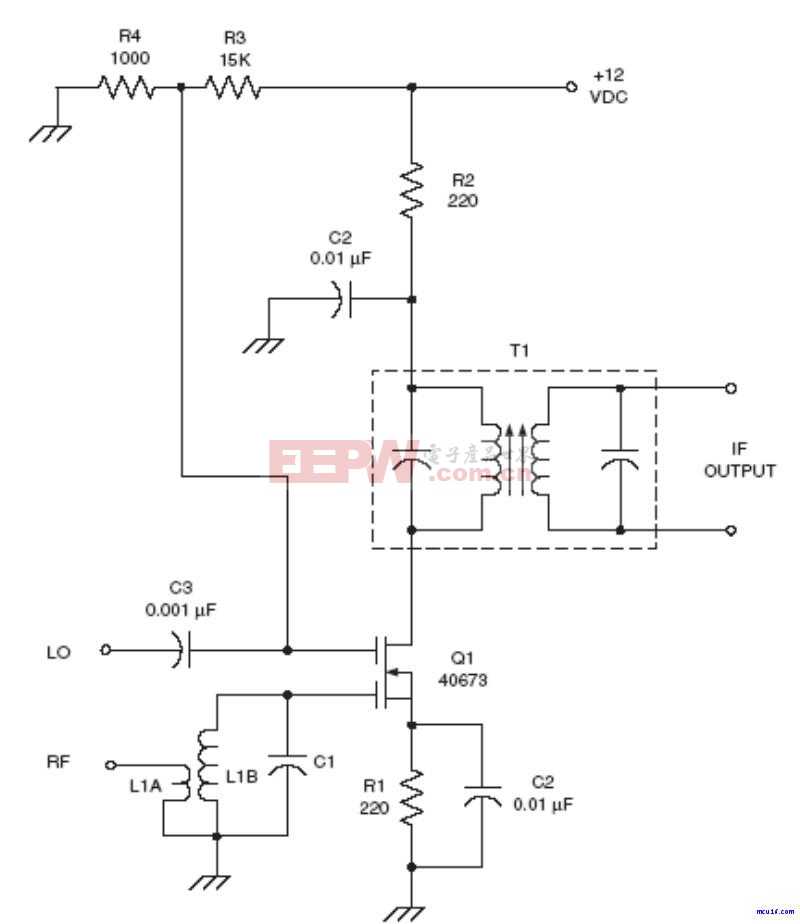

| 图一 : AI芯片的应用案例。(source: Graphcore、Bitmain及Mythic提供) |

事实上,AI市场可以说相当活跃,目前已有超过50家新创公司以及25家传统半导体大厂,都争相抢食AI市场的市占率。由于AI相关厂商的快速成长,使得市场竞争也日趋激烈。对这些厂商来说,产品的上市时间相当重要,因此设计流程中的每一个细节,包含IC测试与芯片调校等过程,都必须把『尽快将质量最好的芯片送到客户手中』当作策略目标。

更快的AI芯片设计工具

大多数AI开发都是从数学算法开始的。开发人员在数学工具中创建算法,并将其转换为C语言,然后在处理器上运行该算法。在这样的过程中,工程人员会发现算法的某些部分能以最佳方式运行,至于其他部分则运行速度较慢。

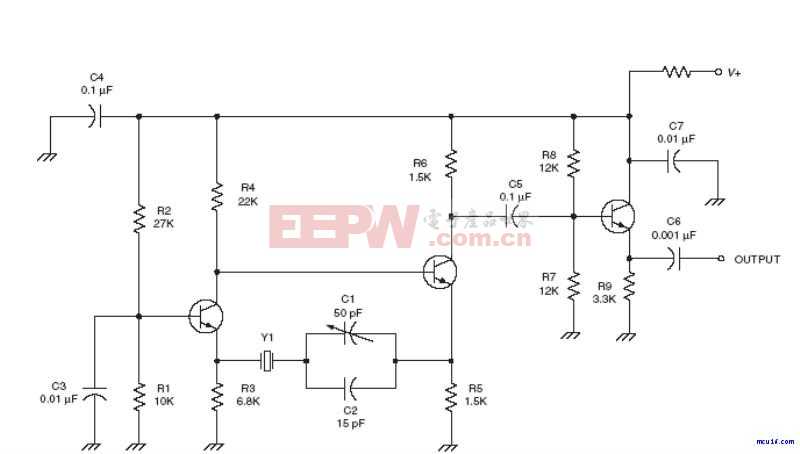

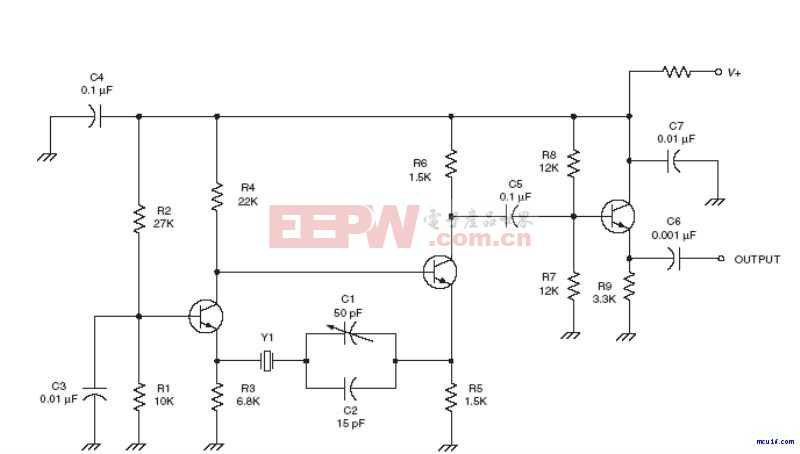

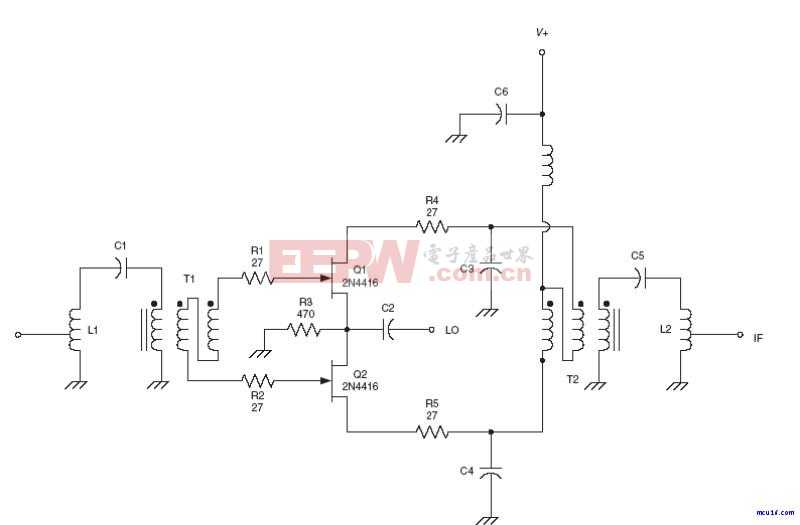

| 图二 : Tessent阶层式DFT让完整的DFT sign-Off能在设计阶层架构的不同层级进行。(source: Mentor Graphics) |

因此,这样的发现使得AI加速器的IP和芯片开发上出现了巨大的成长。工程人员可以强制某些算法透过C语言的调整,使其在现有的ASSP架构上运行,但可能会降低性能和功耗。至于某些算法则需要特别的逻辑性才能进行最佳运算,例如在行动设备上的ML演算。

AI芯片虽然可能有不同的架构,但通常有几个关键的设计特性是共享的。通常AI芯片架构与测试要求对DFT实作策略会产生影响。无论使用的架构为何,AI芯片通常都具有以下的设计特性:

‧闸极数量达数十亿的大型设计。

‧大量经过复制的处理核心。

‧分散的内存。

为特定应用程序开发正确的AI架构,这样的需求也正驱使着EDA工具日新月异,让相关厂商能够开发更高等级的解决方案,现阶段许多厂商都正尝试开发用于AI的SoC,使得EDA厂商的相关业务也都出现了成长。

Mentor Graphics开发的Catapult HLS平台,让AI架构师可以将开发完成的数学算法转换成为C或SystemC等语言,并预先了解如何透过软件与硬件来达到AI演算的最佳结果,并将这些AI架构更完美地应用到实时的AI装置上。

利用AI芯片的规则度

AI系统必须快速处理大量数据,这就需要使用快速的运算能力。这也催生了AI芯片这个快速成长且充满竞争的新市场。

AI芯片通常具有大量相同的核心,利用AI芯片的规则度进行可测试性设计(DFT),代表DFT作业(包含测试插入、测试向量产生以及验证等)只会在核心层级完成一次。然后经过sign-off的完整核心会自动进行复制,以完成芯片层级的DFT实作。Mentor Graphics表示,Tessent阶层式DFT是相当理想的解决方案,除了能利用AI芯片的规则度,并允许在不同的层级对区块进行完整的DFT sign-off。

对于AI芯片来说,以最快的速度将芯片推出市面是首要目标。要满足这项要求,DFT解决方案必须能够支持三项关键功能:

‧利用AI芯片的规则度

‧在RTL中进行DFT插入

‧消除DFT到测试的迭代

Tessent的RTL(register-transfer level)型阶层式DFT与Tessent SiliconInsight方案,能够缩减DFT与芯片调教所需的时间。Tessent的RTL型阶层式DFT,可利用AI芯片的规则度,完成核心层级的DFT sign-off,以及IJTAG的核心复制与整合。RTL型阶层式DFT支持DFT的插入与验证,以及RTL层级的可测试性分析,进而加速设计开发周期。使用这项解决方案,用户的测试向量产生速度能提高10倍,向量缩减量能达到2倍,系统内存使用量则能够减少10倍。

结语

既然AI的宝箱已经被开启,我们所需要的就是用正面与积极的态度来拥抱它。毫无疑问的,在2020年,AI芯片与系统的设计与部署,也将会随着EDA工具的成熟与完备,而继续成长茁壮。

评论