集成式收发器支持实现小型相控阵雷达平台

摘要

本文引用地址:https://www.eepw.com.cn/article/202004/411819.htm相控阵雷达系统利用多个发射和接收通道来实现正常运行。以前,这些平台在构造时都使用独立的发射和接收集成电路(IC)。这些系统在发射(Tx)电路的数模转换器(DAC)和接收(Rx)电路的模数转换器(ADC)中分别使用单独的芯片。这种区分使得许多系统尺寸庞大、成本高昂且功耗高,如此才能获得所需的通道数量,进而发挥所需的功能。由于制造和校准过程复杂,这些系统通常也需要很长时间才能上市。但是,最近出现一种利用集成收发器的方法,它将许多曾经被认为完全不同的功能融合到单个IC之中。这些IC助力实现了小尺寸、低功耗和低成本、具有高通道数量的相控阵雷达系统,且上市时间更短。

集成式收发器简介

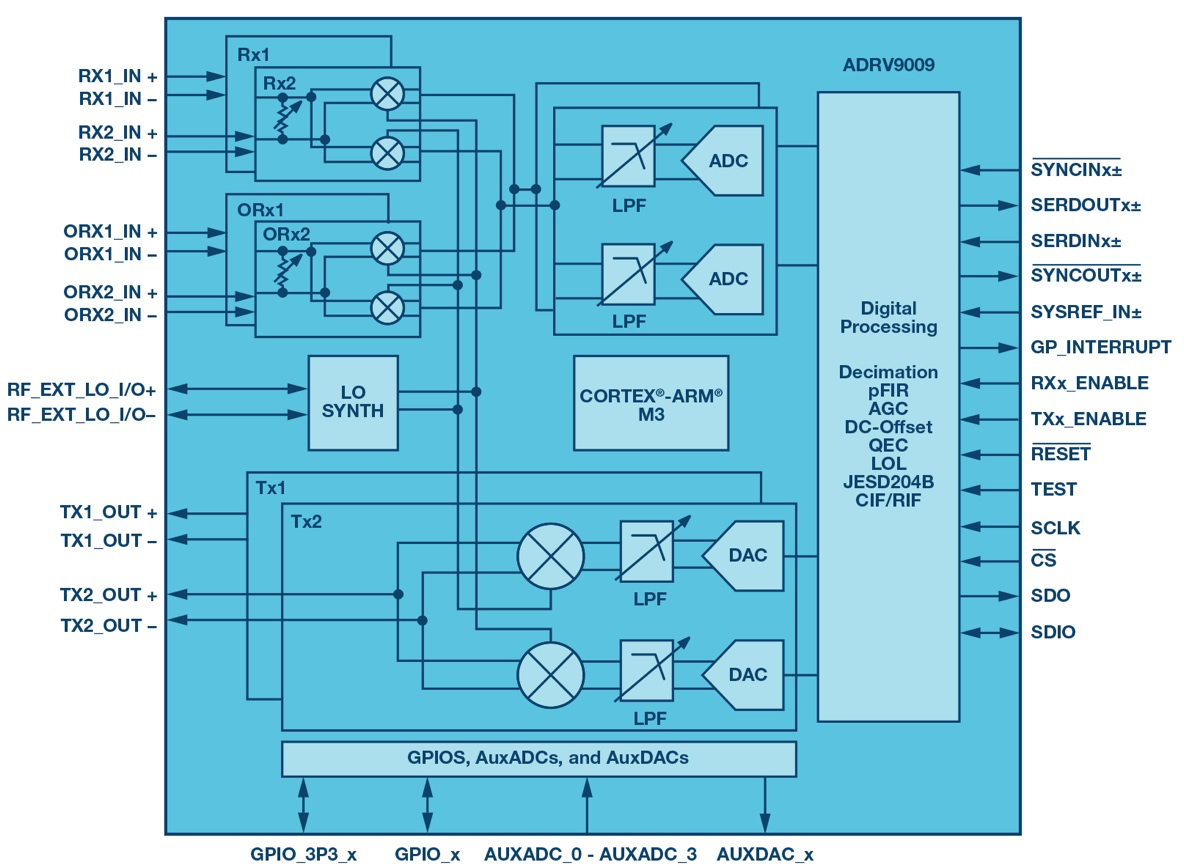

集成式收发器(例如图1所示的收发器)将多种功能集成到单个IC上。例如,新型收发器将DAC、ADC、本振(LO)频率合成器、微处理器、混频器,以及更多功能集成到12 mm × 12 mm单芯片产品中。此外,该产品还集成了两个接收通道和两个发射通道,以及多个数字信号处理(DSP)组件,以获得系统所需的瞬时带宽。还提供一个应用程序接口(API),用于操作客户平台上的收发器。可以利用片内前端网络实现增益和衰减控制。内置的初始化和跟踪校准例程用于提供许多通信和军事应用所需的性能。

图1.ADRV9009是将多种功能集成到单个IC中的集成式收发器示例。

这些集成式收发器能够通过注入一个称为 REF_CLK 的参考时钟信号来创建发射器和接收器所需的所有时钟信号。然后,由片内锁相环(PLL)合成 DAC/ADC 采样、LO 生成和微处理器时钟所需的所有时钟。如果内部LO相位噪声不足以满足客户的应用需求,用户可以选择注入自己的低相位噪声外部 LO。

来自部件的数据经由标准化的JESD204b多千兆串行数据接口进行卸载。这个接口支持同时接收和传输大量数据。新集成式收发器解决方案可以帮助提供接口IP,帮助客户加快上市时间。如果需要确定性延迟和数据同步,用户可以利用内置的多芯片同步(MCS)特性,并发出SYS_REF信号作为初始通道对齐序列(ILAS)的主时序基准。1

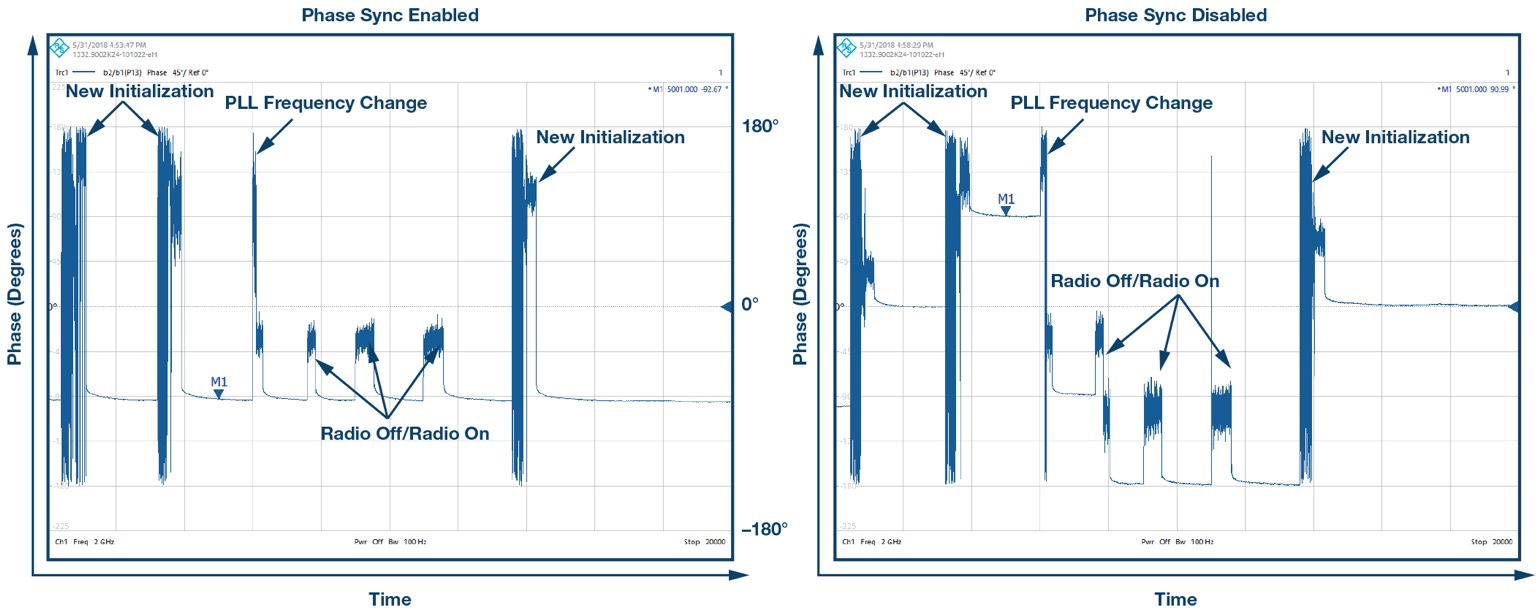

此外,可以利用内置的RFPLL相位同步特性,将发射或接收通道的LO相位设置为相对于主参考相位具备确定性。通过利用MCS和RFPLL相位同步特性,可以在初始化部件、频率调谐,或者开关软件上的无线电时复制相位对齐。图2显示了一个新型集成式收发器示例,该收发器提供决定性相位,且支持所有这些特性。

图2.内置RFPLL相位同步特性让系统与主参考源之间呈确定性相位关系。

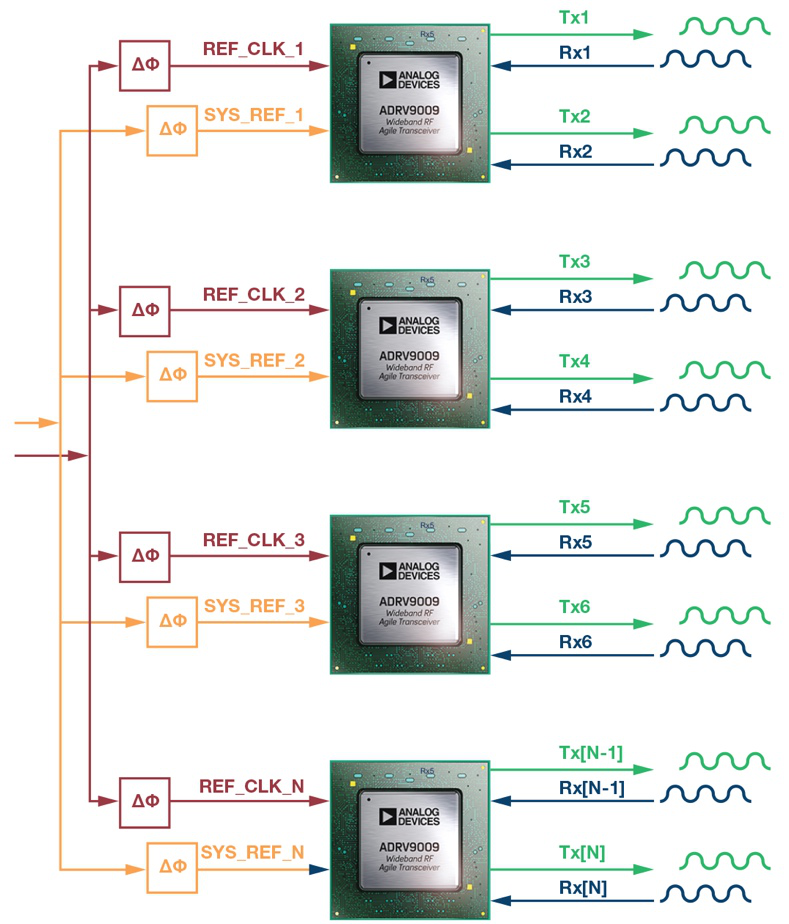

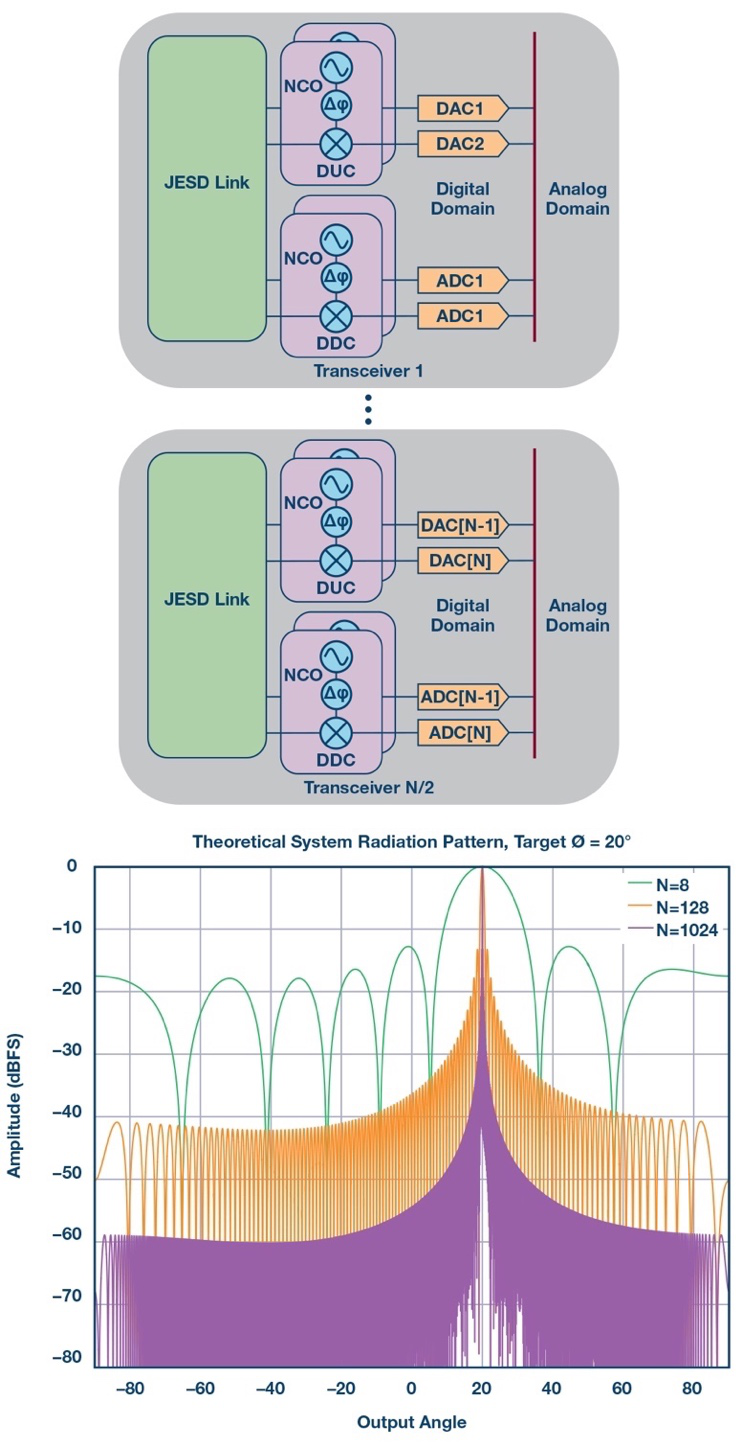

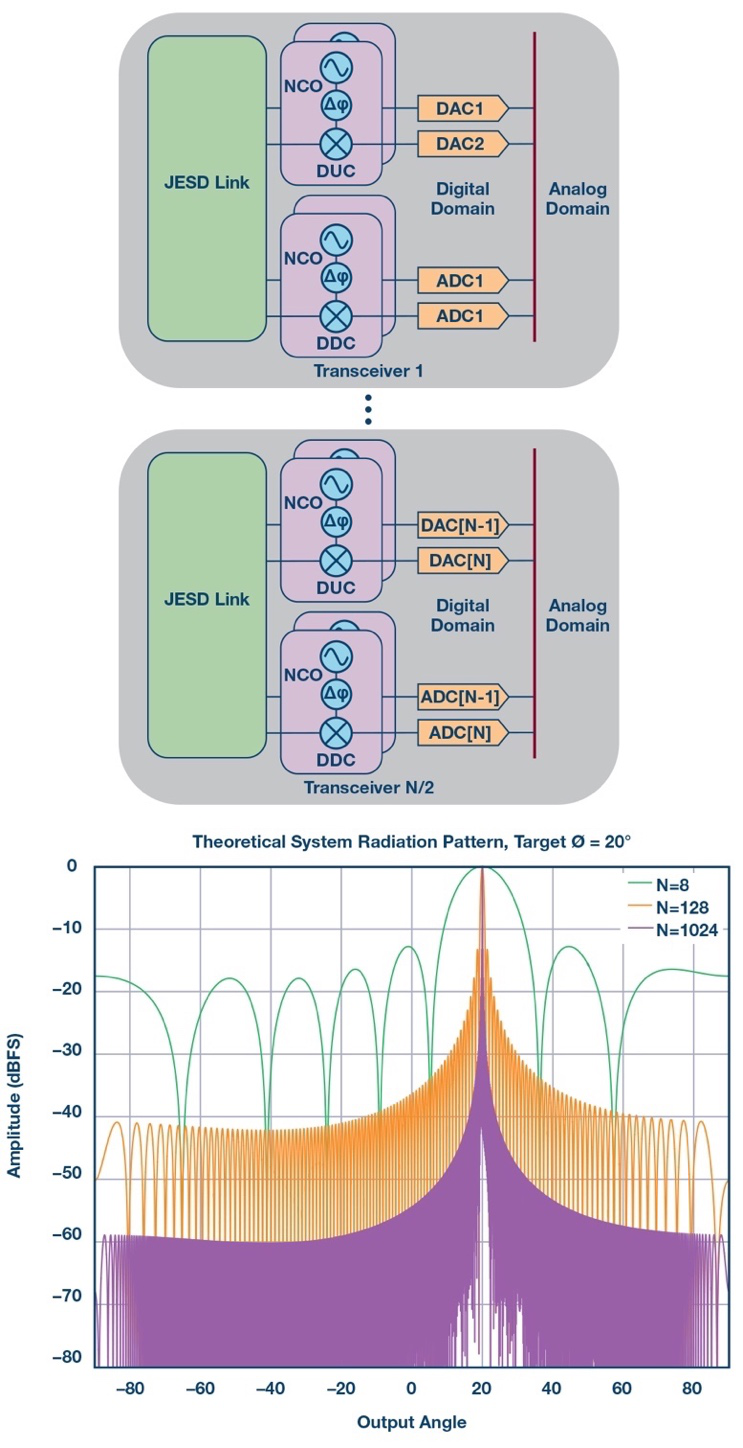

图3.可使用多个集成式收发器来增加系统的通道数量。

使用多个集成式收发器

如果系统需要两个以上接收器和两个发射器,用户仍然能使用多个集成式收发器,从因为单芯片接收和发射通道实现的小尺寸中获益。该技术的示例如图3所示。可以通过使用并发型 SYS_REF 脉冲来同时触发所有IC的内部分压器,从而同步多个集成式收发器。这些 SYS_REF 脉冲可由时钟芯片或基带处理器发出,附带可编程延迟,该延迟是造成各IC之间的路径长度不匹配的原因。跨多个芯片的数据路径和多个LO都可以是确定性的。

集成式收发器是支撑相控阵雷达平台的中坚力量

通过使用同步集成式收发器来增加通道数量,让这些器件成为支撑相控阵雷达平台的中坚力量。结合相位和幅度对齐的发射和接收通道时,使用多个集成式收发器可以展示系统级的动态范围、杂散和相位噪声改善。

片内DSP特性,例如数控振荡器(NCO)和数字上变频器,或者数字下变频器(DDC),现在支持在单个IC内采用系统级杂散去相关方法。2

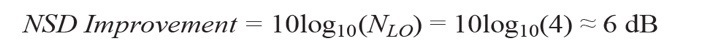

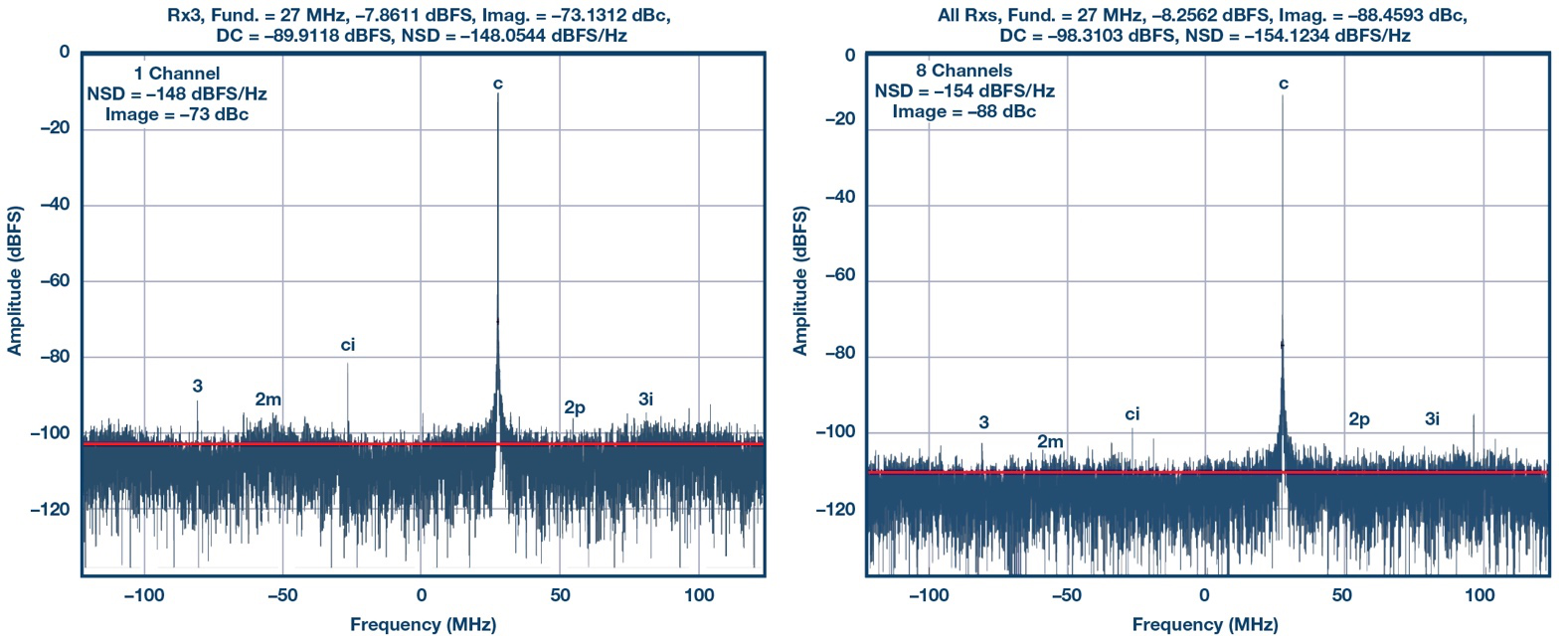

通过使用多个集成式收发器来组合收发器通道,用于展示系统级噪声谱密度(NSD)和杂散性能都得到改善。此举通过降低系统的有效本底噪声,同时维持通道的全部功能来改善相控阵雷达系统的动态范围。图4显示了在集成多达8个集成式收发器接收通道,有效增加相控阵系统中的位数之后,得出的系统级测量结果。注意,从一个通道增加到八个通道时,NSD和计算得出的本底噪声(在各图中用红线表示)将增加6 dB。这是因为,虽然总共有8个通道,但是在用于创建这8个通道的4个集成式收发器中,只存在4个不同且不相关的LO(也就是说,NLO = 4)。

因此实现了如下改善

得出的结果与集成式收发器提供的实验性结果相近。此外,多余的成像频率以不相关的方式聚合汇总,实现系统级杂散性能改善。随着通道数量增加,性能会实现进一步改善,从而实现可扩展的系统。

图4.使用ADRV9009集成式收发器来集成接收通道可以降低噪声谱密度,并改善动态范围。

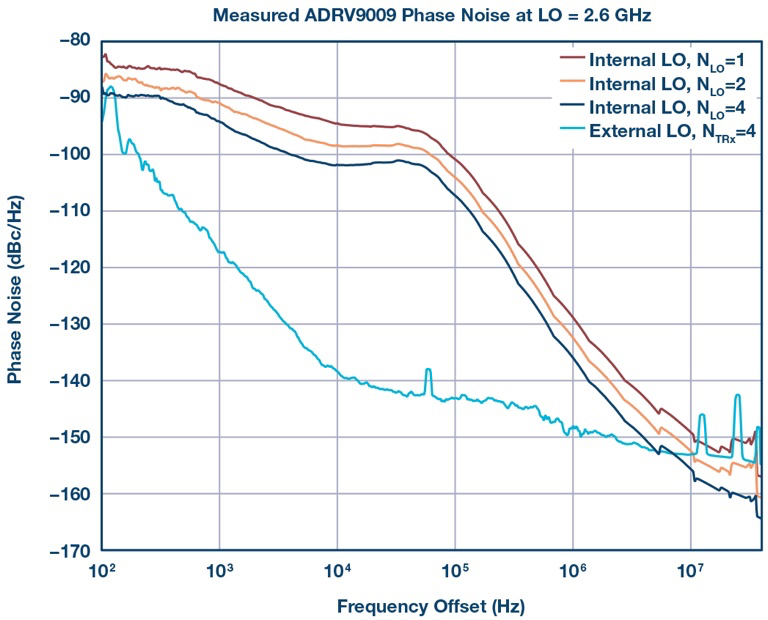

此外,在对齐相位和集成多个集成式收发器通道之后,相控阵系统的相位噪声可以得到改善。从图5最上方的三条曲线显示的测量结果可以看出,在利用4个集成式收发器IC的内部LO组合8个通道之后,相位噪声性能得到了改善。再重复一遍,存在4个不同且不相关的LO(也就是说,NLO = 4)时,当从1个发射通道增加为8个发射通道时,相位噪声会增加6 dB。增加通道数量可以进一步增加相控阵雷达系统的相位噪声。或者,可以将外部LO注入到由NTRx集成式收发器构成的每个子阵列中,并从子阵列层级改善初始相位噪声(如图5中的蓝色曲线所示)。但是,如此一来,该子阵列中的各元件因为都共用同一个LO源,就会互相关联,所以无法自行在子阵列中提供通道聚合改善。对于图5所示的外部LO相位噪声数据,其中使用了一个Rohde & Schwarz SMA100B信号发生器作为外部LO源。

图5.使用内部LO时,集成多个ADRV9009的发射通道可以改善系统级相位噪声性能。

注入外部LO会改善子阵列的初始相位噪声。

图6.DSP特性现在可以利用片内NCO和DDC/DUC实现数字相移。

增加通道数量,优化相移会使集成式收发器形成宽度变窄的波束。

集成的DSP特性(例如NCO、数字移相器和DUC/DDC)允许在数字域内实施基带相移和频率位移,进而允许在基于多通道、集成式收发器的相控阵雷达系统中实施数字波束成型。将多个功能集成到单个IC上之后,系统现在能够在许多相关的相控阵应用中,利用集成式收发器实现天线点阵间隔。利用更多收发器来增加通道数量一般可以让波束变窄,但会导致系统变大。但是,现在将多个功能集成到单个IC之后,系统变大的比例还是要小于过去。使用MATLAB®模拟辐射图之后,图6显示通道数量从N = 23增加到N = 210时,波束如何变窄,理论波瓣幅度如何变深。实际的功率零点将在天线设计中表明。

结论

在单个IC中集成多个数字和模拟功能可以实现更小型的相控阵雷达系统。这些系统支持实施数字波束成型和混合波束成型,具体取决于系统规格。已经证明使用ADI公司提供的 ADRV9009 可以实现系统级性能改善。这些集成式器件让许多新系统能够使用相同的硬件来运行多个应用。

参考资料

1 Harris, J. 什么是JESD204标准,为什么我们要重视它?ADI公司技术文章,MS-2374,1-4。2013年10月。

2 Delos, P.、Jones, M.、Robertson, M. RF收发器支持在数字波束成型相控阵内实施强制杂散去相关。ADI公司技术文章。2018年8月。

作者简介

Mike Jones是ADI公司航空航天和防务部的首席电气设计工程师,在美国北卡罗来纳州格林斯博罗工作。他于2016年加入ADI公司。从2007年到2016年,他在北卡罗来纳州威尔明顿的通用电气公司工作,担任微波光子学设计工程师,致力于研发核工业微波和光学解决方案。他于2004年获得北卡罗来纳州立大学电气工程学士学位和计算机工程学士学位,2006年获得北卡罗来纳州立大学电气工程硕士学位。

Peter Delos是ADI公司航空航天和防务部的技术主管,在美国北卡罗莱纳州格林斯博罗工作。他于1990年获得美国弗吉尼亚理工大学电气工程学士学位,并于2004年获得美国新泽西理工学院电气工程硕士学位。Peter拥有超过25年的行业经验。其职业生涯的大部分时间花在高级RF/模拟系统的架构、PWB和IC设计上。他目前专注于面向相控阵应用的高性能接收器、波形发生器和频率合成器设计的小型化工作。

评论