基于ARM Cortex-M3的SoC系统设计

作者 杨斌1,2,韩瑞欣3,董苏惠4(1.中科院微电子研究所,北京 100029;2.中国科学院大学,北京 100049;3.中科院声学所,北京 100190;4.中科院空间中心,北京 100190)

本文引用地址:https://www.eepw.com.cn/article/201901/397273.htm摘要:本项目实现了一种基于CM3内核的SoC,并且利用该SoC实现网络数据获取、温度传感器数据获取及数据显示等功能。在Keil上进行软件开发,通过ST-LINK/V2调试器进行调试,调试过程系统运行正常。在Quartus-II上进行Verilog HDL的硬件开发设计,并进行IP核的集成,最后将生成的二进制文件下载到FPGA开发平台。该系统使用AHB总线将CM3内核与片内存储器和GPIO进行连接,使用APB总线连接UART、定时器、看门狗等外设。

0 绪论

项目背景与意义

现今,单片机的发展速度特别快,种类越来越多,而对于单片机的选择主要是根据具体的应用情况来定,在性能、功耗、成本上做折中。

目前,FPGA的集成度越来越高,价格也越来越便宜,所以可以以较低的成本来构建专用的片上系统。单片机作为片上系统的一种,可以很容易的在FPGA上实现,并且架构和片上外设都可以根据具体的应用情况随时做出更改,这极大的降低了成本,也规避使用通用单片机所带来的风险。综上,在某些领域,以FPGA作为平台构建专用片上系统是最合适的选择,这也是以后单片机应用领域的发展趋势。研究SoC的设计方法和工程应用对于未来单片机应用领域的革新具有深刻的意义。

内容及章节安排

本项目实现了一种基于CM3内核的SoC,并且利用该SoC实现网络数据获取、温度传感器数据获取及数据显示等功能。

本文共分为五部分,第一部分绪论简单介绍了本项目的背景及意义。第二部分说明了本项目的整体框架设计。第三部分介绍了SoC设计的总体思路。第四部分讨论了软件开发的大体流程。第五部分对未来项目的方向做出了展望。

1 系统整体框架

1.1系统设计流程分析

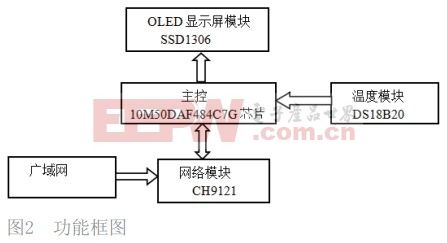

本系统采用的FPGA板卡芯片由Intel PSG(英特尔可编程解决方案事业部,前身为Altera公司,Altera于2015年被Intel收购)生产,所以需要在Quartus-II专用开发平台上进行SoC的硬件设计。Keil软件开发平台界面友好,功能强大,兼容ARM公司发布的所有内核库,包括本系统使用的CM3内核库,并且其支持多种硬件调试和下载器,所以在本项目中使用Keil进行软件开发。软件编译成功后生成二进制可执行文件,并通过ST-LINK/V2调试器进行下载及调试,调试过程系统功能正常。CM3内核使用AHB总线与外设连接,所以该SoC的设计采用AHB总线将内核与片内存储器和GPIO进行连接,使用APB总线连接UART、定时器、看门狗等外设,而APB总线上的外设通过AHB-APB总线桥接器与内核进行数据交互与应答。在Cortex-M3 DesignStart Eval开发套件中提供了本系统用到的基本总线外设,使用Verilog HDL编写了其他组件来实现整个系统的集成。片上系统设计框图如图1所示,功能框图如图2所示。

本项目的功能框图如图2所示。

1.2 模块选择

根据系统的网络数据获取及室内温度显示等功能要求,本项目选择特定模块来实现相应功能。网络模块需要从广域网络中获取数据,并将获得的数据传给SoC平台,该网络模块的默认接口应该是串口,从网络中获取的数据主要是温度数据,数据的传输速率要求不高,尽量选择价格便宜、低功耗的网络模块。室内温度的获取依赖于温度传感器,本系统对于温度的测量精度要求不高,所以温度传感器需具有接口简单、价格便宜、性能稳定等特点。为了做到系统数据的可视化,在设计时候考虑添加OLED显示模块,OLED模块选择具有功耗低、屏幕小、价格便宜等特点的型号。

2 系统硬件设计

2.1 存储器设计

存储器映射

CM3的寻找空间大小是4 GB,代码段和数据段在存储空间上是分开的,外设相关的寄存器也有相应的地址段,内核操作相关的寄存器也占据部分地址空间。本系统采用把程序放到代码区的设计,从而使取指和数据访问操作使用自己的总线。

CM3只有一个单一固定的存储器映射。在Cortex-M3预定义的存储器地址映射中,Code区的地址从0x00000000到0x1FFFFFFF,本系统使用的地址空间从0x00000000开始,结束地址是0x0000FFFF,大小为64KB。内部SRAM区的地址空间从0x20000000到0x3FFFFFFF,本系统使用的地址从0x20000000开始,结束地址是0x20000FFFF,大小为64 KB。

该子系统是基于APB总线,内部涵盖系统用到的大部分外设,内部外设的地址划分见下表1。

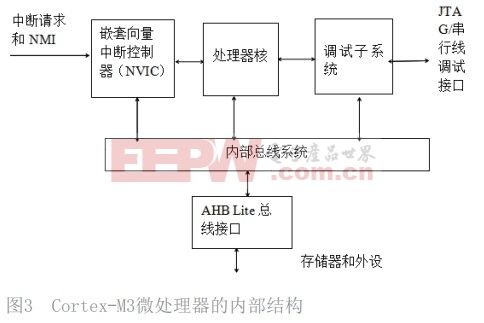

2.2 Cortex-M3的结构

Cortex-M3微处理器的内部结构如图3所示。ARM Cortex-M3微处理器包括:处理器核、嵌套向量中断控制器(NVIC)、调试子系统、AHB LITE总线接口以及连接这些单元的内部总线系统。

2.2.1 处理器核

处理器核是Cortex-M3最核心的功能部件,它负责对数据进行处理。

本项目Cortex-M3处理器内核采用3级流水线操作。流水线的3级分别是:取指,解码和执行。

2.2.2 嵌套向量中断控制器

专用的 NVIC用于对中断进行管理,并且向处理器核发出中断请求信号,包含最多240个中断请求,以及1个不可屏蔽中断。NVIC是与CPU紧密耦合的,它还包含了若干个系统控制寄存器。

2.2.3 总线系统

总线系统用于将Cortex-M3内部的各个功能部件连接在一起。总线系统包括:①内部总线系统;②处理器核内部的数据通道;③AHB Lite接口单元。

2.2.4 调试子系统

作为Cortex-M3处理器重要的一部分,调试子系统提供下面的功能。

①管理调试控制、程序断点、以及数据监控点。

②当产生调试事件时,它将处理器核设置为停止状态。此时,可以在该点分析处理器的状态,如寄存器值和标志。

2.3 异常处理与中断向量表设计

Cortex-M3在内核水平上搭载了一个异常响应系统,支持为数众多的系统异常和外部中断。

向量中断控制器(NVIC)以存储器映射的方式来访问,除了包含控制寄存器和中断处理的控制逻辑之外,NVIC还包含了MPU的控制寄存器、SysTick定时器以及调试控制。

2.4 地址译码器和多路复用器设计

本系统基于AHB-Lite所构建的Cortex-M3 SoC系统设计包含了地址译码器和多路复用器。

在系统中,来自不同从设备的响应信号,包括:HRDATA、HREADY和HRESP连接到多路复用器的输入,根据地址译码器所生成的选择信号,多路复用器将选择的从设备响应信号送给主设备。其中HRDATA[31:0]是来自多路复用器到主设备的读数据,由多路复用器指向主设备;HREADY是来自多路复用器到主设备的准备信号,由多路复用器指向主设备和从设备,当该位为高时,该信号表示到主设备和先前完成传输的所用从设备。

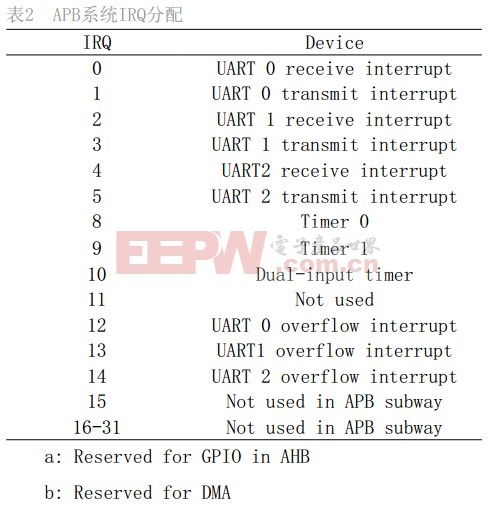

2.5 APB子系统

该APB子系统的顶层是AHB-Lite总线接口,可以与内核的AHB总线进行连接。子系统内部包括的外设有定时器、UART、双输入定时器、看门狗电路、AHB到APB的桥接器、异步中断信号等。表2为APB系统IRQ分配表。

2.6 时钟和复位电路设计

本系统片上SoC系统主要包含HCLK、PCLK、PCLKG等三个时钟,HCLK时钟主要用于内核的工作时钟以及驱动片内高性能总线上挂载的外设。PCLK时钟主要用于驱动APB子系统内挂载在高性能外设总线上的大部分外设。PCLKG时钟是当子系统内部的外设无任何活动的时候,通过子系统的APBACTIVE信号可以控制该信号的输出,以实现降低功耗的目的。

系统的复位信号有两种,第一种是系统采用FPGA外部管脚控制系统复位,低电平复位的方式;第二种是系统异常请求复位,该复位发生在系统程序运行错误或者硬件错误的情况下。

3 软件系统设计

3.1 CMSIS原理及设计

CMSIS提供了标准的软件接口,如库函数。

使用CMSIS后,一切都标准化了,主要体现在以下几点:

一是使用标准化函数访问NVIC、系统控制块(SCB),以及系统滴答定时器SysTick。

二是使用标准化函数访问特殊寄存器。

三是使用标准化函数访问特殊指令。

四是标准化的系统初始化函数名字。

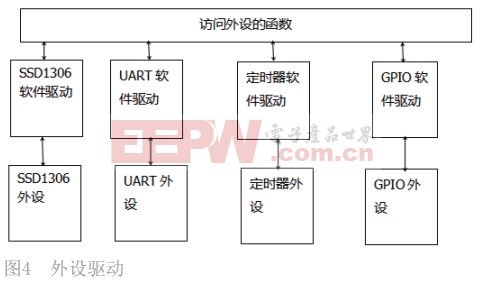

3.2 SoC外设驱动设计

如图4所示,设计AHB外设驱动的要求包括以下几点:①为每个外设编写软件驱动程序;②不需要操作系统支持;③软件驱动程序应该提供基本的功能,用于简化外设的访问。

3.3 SoC中断寄存器管理

中断分组设置函数,void NVIC_ Configuration()中断配置函数,在这个函数里面只调用了固件库的中断分组配置函数,整个系统的中断分组组别为2。这个函数在系统初始化的时候调用即可,并且永远只需要调用一次,示例如下所示。

void NVIC_Configuration(void)

{

NVIC_PriorityGroupConfig(NVIC_PriorityGroup_2);//设置NVIC中断分组2:2位抢占优先级,2位响应优先级

}

3.4 系统模块及程序设计原理

3.4.1 温度模块

DS18B20与传统的热敏电阻相比,其能够直接读出被测温度并且可根据实际要求通过简单的编程实现9~12位的数字值读数方式。

当DS18B20接收到温度转换命令后,开始启动转换。转换完成后的温度值就以16位带符号扩展的二进制补码形式存储在高速暂存存储器的第1、2字节。单片机可通过单线接口读到该数据,读取时高位在后、低位在前,数据格式以0.0625 ℃/LSB形式表示。

3.4.2 显示器模块

OLED显示器是一种由有机分子薄片组成的固态设备,施加电力之后就能发光。OLED能让电子设备产生更明亮、更清晰的图像,其耗电量小于传统的LED显示屏。

3.4.3 网络模块

网络模块采用CH9121,CH9121 是一款网络串口透传芯片。CH9121内部集成TCP/IP协议栈,可实现网络数据包和串口数据的双向透明传输,具有 TCP CLIENT、TCP SERVER、UDP CLIENT 、UDP SERVER 4 种工作模式,串口波特率最高可支持到 921600bps,可通过上位机软件或者串口命令轻松配置,方便快捷。

4 结论

在后续的设计过程中,我们会在系统中添加指纹模块,利用指纹识别技术可以实现现代智能家居的安防。通过指纹识别技术可以对用户指纹进行精准识别,防止未注册陌生人的入侵。同时也会添加摄像头模块,利用摄像头模块进行人脸识别,可以判断当前采集的人脸头像是否在原有的数据库里,与数据库信息进行比对,来判断是否有非法闯入。

此外,为了更好地实现智能化,我们会将居家生活中的各种用电器接入系统中来,通过继电器开关来实现开关中断,这样可以实现远程操控用电器的功能。

参考文献

[1]Cortex-M3权威指南(中文)手册,2017.

[2]CM3技术参考手册,2017.

[3]DE10-Lite_User_Manual handbook,2017,1.

[4]王永虹,徐炜,等.STM32系列ARM Cortex-M3微控制器原理与实践.北京航空航天大学出版社, 2008.

[5]STM32开发指南——库函数版本手册,2016.

作者简介:

杨斌 (1994-),男,研究生,主要从事嵌入式系统开发及信号处理的研究。

韩瑞欣 (1994-),男,研究生,主要从事射频RFID的研究。

董苏惠 (1994-),女,研究生,主要从事卫星组网通信的研究。

本文来源于科技期刊《电子产品世界》2019年第2期第55页,欢迎您写论文时引用,并注明出处

评论