Mentor 宣布推出适用于三星 8LPP 和 7LPP 工艺技术的工具和流程

Siemens 业务部门 Mentor 今天宣布,已与三星电子合作推出各种适用于三星 8LPP 工艺技术的 Mentor 设计和验证工具及流程。在 EUV 光刻时代到来之前,最具竞争力的扩展优势将源于 8LPP。相较于 10LPP 工艺,8LPP 的性能实现了进一步提升。针对 8LPP 推出的工具包括 Calibre® 物理验证套件、Mentor® Analog FastSPICE™ (AFS™) 定制和模拟/混合信号 (AMS) 电路验证平台,以及 Nitro-SoC™ 布局和布线 (P&R) 电子设计平台。这些 Mentor 解决方案可用于三星 8LPP 工艺技术生产流片的设计和 Sign-off。

本文引用地址:https://www.eepw.com.cn/article/201706/359956.htm此外,Calibre 套件的核心模块现可支持使用 EUV 光刻的 7LPP 工艺技术,其中包括 Calibre nmDRC™、Calibre nmLVS™、Calibre xACT™ 和 Calibre PERC™ 软件。这些 Calibre 设计套件可用于三星 7LPP 工艺技术的初始测试芯片和知识产权 (IP) 创建。

“三星代工厂将一如既往地提供业界最具竞争力的工艺技术。我们与 Mentor 之间的协作可确保推出合格的工具,从而让我们的共同客户能够充分利用三星代工厂的工艺产品,并开发出卓越的设计,”三星电子代工厂设计部门高级副总裁 Jaehong Park 说道。“Mentor 推出适用于 8LPP 和 7LPP 的工具,是我们双方长期合作关系的有力佐证,并且我们将继续携手共进,力争让设计人员可以胸有成竹地实施、验证、测试和交付设计。”

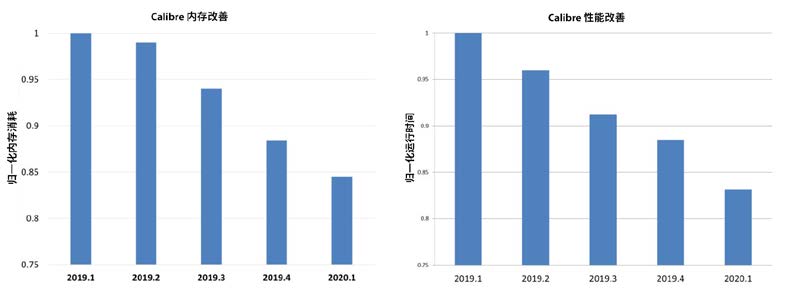

业界领先的 Calibre 平台中已涵盖多种适用于 8LPP 工艺技术的工具,三星也已经开始启用这些工具,以此确保设计人员能够快速从容地成功完成流片。

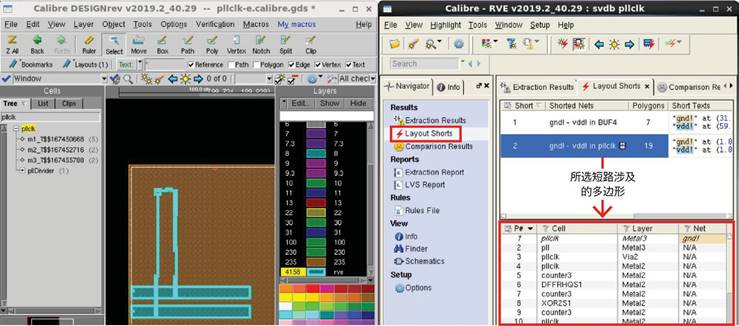

· Calibre nmDRC 和 Calibre nmLVS 工具可帮助设计团队验证和优化其设计,以满足三星 8LPP 工艺要求。这两种工具提供了准确的创新型物理和电路验证功能,可应对日益增长的版图复杂性和严苛的先进节点设计性能要求。

· Calibre Pattern Matching 功能可以让设计人员应用各种可视性几何图形分析,快速准确地执行复杂的验证任务,例如跨多个实例且对配置有精确要求的验证,以及光刻热点识别。

· Calibre xACT 平台提供了无可匹敌的寄生参数提取精度和性能,可自动使用集成的场解算器来计算(以阿托法拉级的精度)复杂三维结构的寄生参数,同时采取可高度扩展的并行处理方法为包含数百万实例的设计优化性能。

· Calibre PERC 可靠性平台采用独特集成的方法对物理版图和网表进行分析,从而自动进行复杂的可靠性检查。

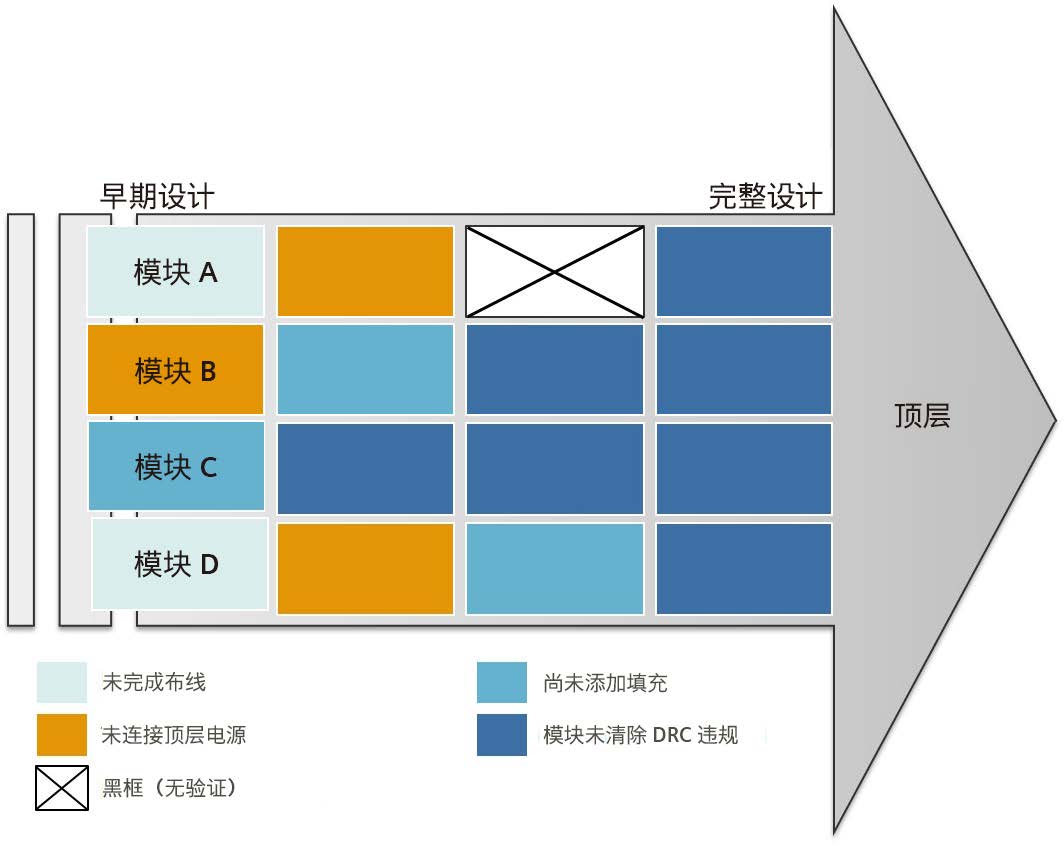

· Calibre YieldEnhancer 产品,特别是其 SmartFill 和工程变更单 (ECO)/Timing-Aware Fill 功能,可帮助设计人员通过知识产权 (IP)、模块和全芯片之间的多项设计变更来控制设计平坦度,从而确保设计能够满足制造工艺平坦化要求,并符合流片排程。它还可以使设计人员能够应用版图布局的增强功能(例如通孔优化),进而提高制造的成功率。

· Calibre LFD™ 工具,基于 Mentor 的工艺窗口建模、掩膜合成、光学邻近效应修正 (OPC) 和分辨率增强 (RET) 的生产部署解决方案,可准确地对光刻工艺的影响进行建模,从而预测实际“已制造好的”版图尺寸,识别潜在光刻问题,以及帮助设计人员优化良率和产品可靠性。

· 由于设计团队可同时处理多个可制造性设计 (DFM) 方案,因此他们可使用配有 Calibre YieldAnalyzer 工具的三星 DFM 评分和分析解决方案来简化折衷决策流程,例如通孔冗余检查。此外,三星还支持整合 Calibre Pattern Matching 解决方案的良率减损图形识别和修正,以便提供从制造成果到客户设计流程的快速反馈。为了进一步确保客户能够快速找到 DFM 问题并予以解决,Mentor 和三星还宣布推出 Calibre DFM Explorer 功能。

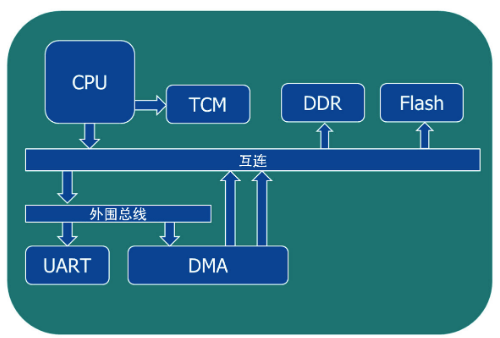

为了让片上系统 (SoC) 设计人员能够胸有成竹地完成电路验证、物理实现和 IC 测试,三星在其 8LPP 设备模型和设计套件中启用了 AFS 平台。我们的共同客户依靠 AFS 平台,在验证模拟、射频、混合信号、内存和定制数字电路上,提供比传统 SPICE 仿真器速度更快的纳米级 SPICE 精度验证。

Nitro-SoC P&R 系统支持在三星 8LPP 工艺技术中进行网表到 GDSII 的物理实现。这个技术节点支持各种创新型技术,包括多重曝光布线层的高级设计规则检查 (DRC) 规避、收敛时序的掩膜和层优化,以及智能库管脚接入功能,因此可获得优化的功率/性能/占位面积 (PPA) 结果。客户能够获取各种功能,包括基于多拐角多模式 (MCMM) 的占位面积优化、基于多 VDD 的全面低功率流程、与 Calibre Sign-off 的本机集成,以及可缩短周转时间的全面并行化。

“我们与三星代工厂的合作并不仅仅是为了提供符合最低要求的工具,”Mentor Design-to-Silicon 事业部副总裁兼总经理 Joe Sawicki 说道。“我们联合推出的解决方案还可让我们的共同客户充分利用三星的工艺产品,以在初始流片和硅生产两方面获得成功,从而在无晶圆厂公司和三星代工厂之间架起至关重要的连接桥梁。”

评论