基于ZYNQ嵌入式小型化继电保护平台设计实现

作者/ 任华锋 王晋华 孙振华 许继电气股份有限公司(河南 许昌 461000)

本文引用地址:https://www.eepw.com.cn/article/201611/340863.htm摘要:本文介绍了一种应用在智能变电站中全新的嵌入式小型化继电保护平台的设计,该设计选用片内集成双ARM内核和FPGA的Xilinx Zynq系列芯片,在成本、数据处理速度、功耗及可扩展性方面能够满足就地化安装继电保护设备的需求。全文从软件和硬件方面详细阐述了嵌入式小型化继电保护平台的设计方法。

引言

随着加强智能电网建设的深入推进,网络信息技术、电子传感技术、数字变电技术、广域测量技术、自动化控制技术等多种先进技术在智能继电保护装置中的应用日趋成熟。在此背景下,智能电网建设对继电保护装置的软硬件设计也提出了更高的要求。继电保护装置的小型化设计和就地化安装就是其中的一种发展趋势。针对这些要求,本文介绍了一种基于Xilinx Zynq 7000系列片上系统(SoC)的嵌入式小型化继电保护平台的设计方法,就该平台的整体框架、硬件设计、平台搭建等方面进行了详细的阐述。

1 平台整体框架

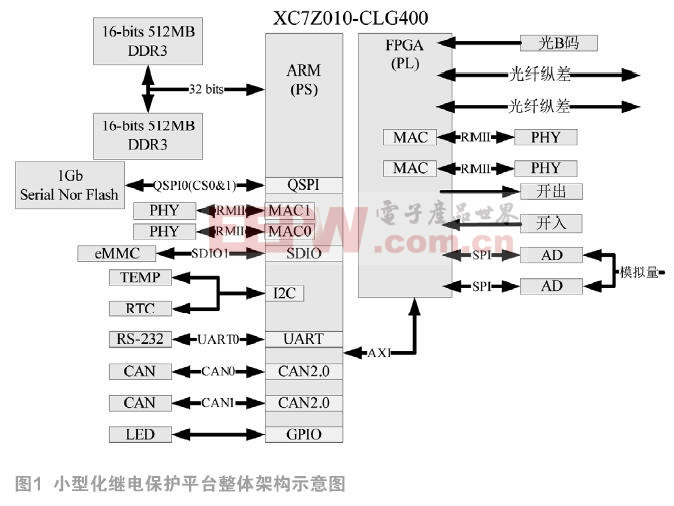

按照国家电网的规划,小型化继电保护装置直接安装在户外一次设备旁,对装置的电磁干扰、工作环境和结构强度等方面提出了更高的要求。本方案采用Xilinx的Zynq 7000系列芯片为主CPU,芯片片内集成了主频800MHz的ARM双核处理器、FPGA、PCIe、I2C、SD/MMC等常用通信接口,具有强大的数据处理和外设扩展能力,特别是功耗低,抗干扰能力强的特点,非常适合作为就地化安装继电保护装置的硬件平台。该平台的整体框架如图1所示。

2 平台硬件实现

Xilinx Zynq 7000根据功能划分为可处理系统(PS)ARM及其外设,可编程逻辑(PL)FPGA。硬件设计主要围绕这两部分展开。

2.1 PS侧

PS侧由ARM核管理、配置I/O外设、DDR控制等。ARM核的应用非常广泛,可供参考的典型硬件设计资料非常多,限于篇幅,只对小型化继电保护平台应用到的部分进行介绍。

2.1.1 DDR内存控制器

大多数智能继电保护设备运行嵌入式实时操作系统,由实时操作系统完成继电保护算法、人机交互,以及基于IEC61850的网络通信等功能。实时系统对DDR内存的容量和处理速度有很高的需求。在设计中使用了两片Micron公司的DDR内存MT41K256M16HA-125-IT:E ,容量达到1G,与ARM核650MHz时钟匹配工作在 525MHz时钟速率。经过Nucleus实时操作系统的测试,系统运行正常。为保证继电保护设备数据的可靠性,DDR内存控制器可增加ECC功能,位宽降为16bit,内存容量降为512M。

2.1.2 I/O外设配置

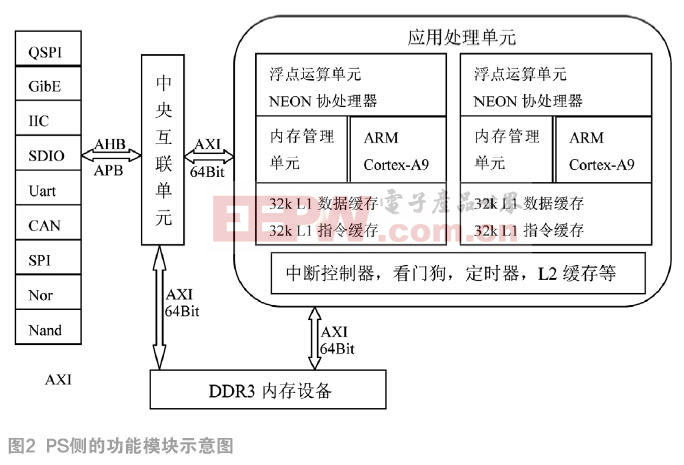

Zynq 的I/O引脚采用多路复用外设接口方式,PS侧的MIO共有54路I/O,可用Xilinx 提供的硬件设计工具Vivado把I/O功能灵活定义成MAC、UART、I2C、CAN、SDIO等平台中需要的外设接口,同时配置外设的工作时钟。图2为继电保护平台在Zynq SoC芯片PS侧的功能模块示意图,其描述了外设和内核之间的数据通道和ARM内核的基本构成。

2.2 PL侧FPGA设计

当前主流继电保护设备厂家生产的智能保护设备硬件平台基本采用“处理器+FPGA” 模式,由FPGA完成人机交互、网络拓展、扩展开入开出、AD采样等功能。这种模式下FPGA和处理器是两个独立运行的系统,实现数据同步和协同工作上处理复杂,在变电站电磁环境恶劣的工作地点容易出现问题。

Zynq将处理器和FPGA集成在芯片内部,ARM双核和FPGA的数据交互通过高性能、高带宽、低延时的AXI总线完成,消除了处理器和FPGA通过扩展总线数据传输速度低的瓶颈。特别是以ARM为主,FPGA为辅的片内协作工作模式,为平台提供了丰富的外设扩展功能。

2.2.1 FPGA网络功能设计

为了设计简化和施工便捷,智能变电站过程层在IEC61850 标准下,SV和GOOSE网络报文由点对点传输方式转向共网方式传输。在Zynq平台上由FPGA的MAC IP核通过以太网PHY扩展出的网口接收合并单元或智能终端发送的SV和GOOSE报文,通过MAC IP核实现报文类型甄别、单播、组播广播报文的过滤,并对SV和GOOSE报文的属性进行解析。为了抑制共网传输的网络风暴,可加入风暴抑制判据,过滤掉异常报文,减轻ARM处理器的工作载荷,提高数据处理的实时性。

2.2.2 继电保护功能模块设计

Zynq充分考虑到在Xilinx FPGA产品上设计的移植性,可将原来“处理器+FPGA”模式下FPGA实现的功能模块方便快捷地移植到Zynq平台上,节省开发时间,保持产品稳定性。

2.2.2.1 人机接口功能实现

由于小型化保护装置采用就地化安装方式,直接暴露在风吹日晒、雨雪环境中,装置密闭性要求达到IP67的防护等级,无法安装液晶、键盘等人机交互器件。区别于通过FPGA扩展液晶和键盘外设的智能保护装置,就地化保护装置人机功能是通过安装在主控室或保护小室的就地化保护智能管理单元来实现装置的界面集中展示、配置管理、备份管理、在线监视和诊断功能,所有数据由就地化保护的网口通过光纤网络上传,抗干扰能力强。

2.2.2.2 常规互感器保护采样功能实现

小型化保护的采样方式有两种:常规互感器采样通过电缆直接连接到小型化保护装置;电子式互感器SV和GOOSE共网通过光纤以太网接入小型化保护装置。在常规互感器采样方式中,小型化保护平台使用两片AD7606共16路采样通道,采集电压、电流等模拟量供保护或测控使用。

AD7606芯片通过串行SPI 和FPGA连接,由FPGA保持采样时序和AD数据正确性,ARM核完成对FPGA采样功能的参数,如每周波采样点数、通道个数、预采样时刻等进行设置,FPGA通过中断方式通知ARM核收取采样数据。这部分功能可由在“处理器+FPGA”模式下用Verilog HDL编写的FPGA代码稍作改动后移植到Vivado Zynq硬件设计工程中。

2.2.2.3 继电保护开入开出回路实现

小型化保护装置由于机箱尺寸受限,不能装设太多的开入开出回路。考虑与非智能的一次开关设备接口,保留了8路遥信开入和8路出口回路来采集信息和控制一次开关设备。Zynq的PS侧的复用MIO多用做外设接口,数量较少,无法实现16路I/O。开入开出设计由PL侧的EMIO来实现,外部开入和PL侧开出都经过总线收发器SN74LVC245,由FPGA编写简单的I/O硬件驱动,通过中断或查询方式通知ARM。

3 软件框架和应用功能实现

嵌入式小型化继电保护平台的软件框架主要包括平台的底层硬件驱动、引导程序、嵌入式实时操作系统和应用功能模块。

3.1 底层硬件驱动

Xilinx 的SDK开发工具提供了针对Zynq的BSP包,BSP包含ARM的外设接口驱动,并提供丰富的测试例程供开发者参考。BSP提供的ARM外设驱动代码用C编写,移植方便,改动量小。FPGA部分设计的网口和AD采集等模块需要在PS侧重新开发相应的驱动。

3.2 平台引导

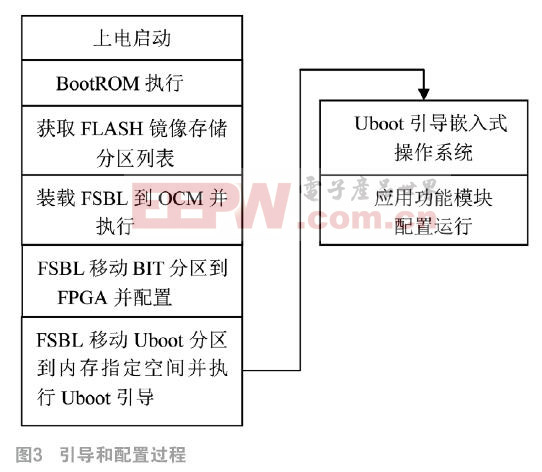

Zynq是以ARM为核心的FPGA,平台引导时,先引导ARM核,由ARM配置引导其他部分。引导的主要内容是引导ARM的实时操作系统和FPGA的BIT配置文件。图3是引导和配置过程的详细列表。

在平台的引导过程中,FSBL加载Uboot到ARM来运行,Uboot提供了ARM外设接口的驱动并完成操作系统启动前必须的硬件初始化,之后将控制权移交给操作系统。启动时烧写到FLASH中的镜像文件可由Xilinx SDK生成,镜像文件包含FSBL的ELF格式可执行文件,FPGA代码编译生成的BIT文件和交叉编译生成Uboot的ELF格式可执行文件。

3.2 平台嵌入式实时操作系统

嵌入式操作系统采用国外引进的支持Zynq 7000系列芯片的嵌入式实时操作系统Nucleus Plus,Nucleus Plus具有实时的、抢先的、多任务的内核。95%的内核代码由C语言编写,移植性好,以后可以平滑移植到性能更好的平台之上。开发人员可对Nucleus Plus操作系统进行定制修改,以适应小型化继电保护平台的特殊需求。

考虑到Zynq 7000 ARM双内核的工作方式,在操作系统选型时,选择了支持双核SMP(对称式)的Nucleus Plus。目前,Zynq ARM双核在继电保护设备应用设计中,有的采用AMP(非对称式)方式,即核0搭建 Linux操作系统,处理实时性不高的应用,如IEC61850中的协议解析,设备属性数据处理等;核1处理高实时性的继电保护算法等功能,满足继电保护设备的实时性。相对AMP、SMP模式的操作系统具有可共享内存、较高的性能和功耗比,以及易实现负载均衡等优点,更能发挥多核处理器的硬件优势,并且在跨处理器硬件平台的移植开发上,更容易和快捷。

3.3 应用功能模块

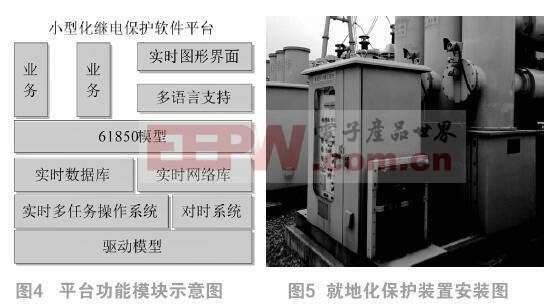

小型化继电保护软件平台采用多模块自动加载管理系统,完全实现通信管理模块、人机接口、系统平台、设备驱动和应用模块的独立编译和下载,并在初始上电过程中,自动识别各软件模块,建立各模块的初始工作环境,自动执行软件模块的相关操作。这样,调试升级或系统功能变化时,只要对相关功能模块进行升级、编译和下载,从而将设计、调试、测试等缩小到一个有限的范围,既缩短了开发周期,又降低了软件开发的难度和复杂度。平台基本功能模块组成如图5所示。

4 结束语

就地安装的小型化保护装置已经在智能变电站中有了试点应用。为了方便安装,装置尺寸设计大约是260mm×180mm×100mm,可以两台并排安装在一次设备汇控柜侧面,不需要专用屏柜。整装置实测功耗最大不超过11W,约是常规智能保护装置的1/4。全密闭式金属机壳结构和免维护设计是智能变电站就地化保护设备发展趋势。

Xilinx Zynq系列芯片已经广泛应用在嵌入式产品的各个领域,在稳定性和可靠性上得到了多种相关产品的验证。在此基础上设计的小型化继电保护平台具有低功耗、低成本、高度集成的优点。特别是片内ARM+FPGA的架构,让该平台能够灵活地拓展外设功能,使系统速度和系统资源得到充分的利用。基于该平台的继电保护产品能够较好地满足当前智能变电站保护测量设备就地化安装的需求,降低智能变电站的建设成本。

参考文献:

[1]刘振亚.智能电网技术[M].中国电力出版社,2010.

[2]王莹.Xilinx可扩展处理平台:ZYNQ嵌入式处理器与FPGA集成的独特创举[J].电子产品世界,2014(2):27-32.

[3]Xilinx Inc.Zynq-7000 All Programmable SoC Technical Reference Manual(v1.0),2015.

[4]何宾. Xilinx all programmable Zynq-7000 SoC[M].北京:清华大学出版社,2013.

[5]陆佳华.嵌入式系统软硬件协同设计实战指南[M].机械工业出版社, 2013.

本文来源于中国科技期刊《电子产品世界》2016年第11期第68页,欢迎您写论文时引用,并注明出处。

评论