Kilopass推出VLT技术,欲改变DRAM产业格局

半导体嵌入式非易失性存储器(eNVM)知识产权(IP)产品提供商Kilopass Technology, Inc.近日推出垂直分层晶闸管(Vertical Layered Thyristor, VLT)技术。该技术显著降低了存储芯片的成本且与DDR SDRAM完全兼容,使用标准CMOS工艺制造且无需昂贵的电容结构。

本文引用地址:https://www.eepw.com.cn/article/201610/311396.htm由于当前基于1个晶体管+1个电容器(1T1C)存储单元结构的DRAM解决方案不够合理,电容器无法进一步缩小,尺寸太大,在20nm工艺上,电容量太低,DRAM技术自2010年以来已放缓了前进的步伐,预计在2017年之前,SoC将在7nm工艺上实现,3D NAND将实现64/96层堆叠,而DRAM将停滞于10nm以上的工艺。Kilopass Technology首席执行官Charlie Cheng介绍道。

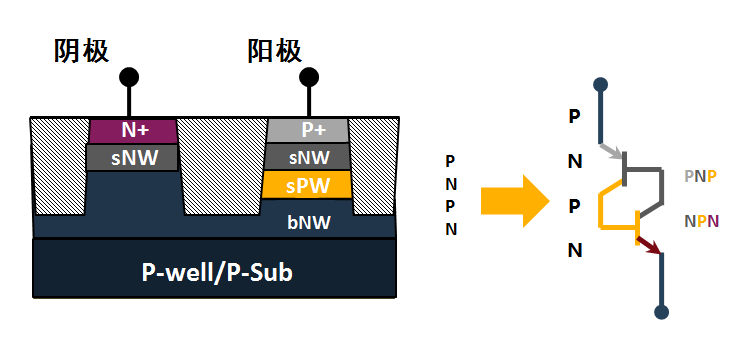

VLT存储器技术省去了传统存储单元中的电容器,采用垂直分层晶闸管结构(如图1),从而使存储单元更紧凑,减小了存储单元的尺寸,同时也省去了数据刷新。由公式(1)和公式(2)对比可见,VLT 8Gb DRAM相较1T1C 8Gb DRAM减小了31%的存储单元面积。

图1 VLT垂直分层晶闸管结构及原理图

1T1C 8Gb DRAM的尺寸为:9.7mm×5.8mm=56.26mm2 (1)

VLT 8Gb DRAM的尺寸为:8.4mm×4.6mm=38.64mm2 (2)

VLT无需新的材料,与逻辑CMOS工艺兼容,存储速度快(十几ps),功耗低(低于0.1pA),“0”和“1”之间的信号区别高达108倍,同时已经经过芯片产品的验证。

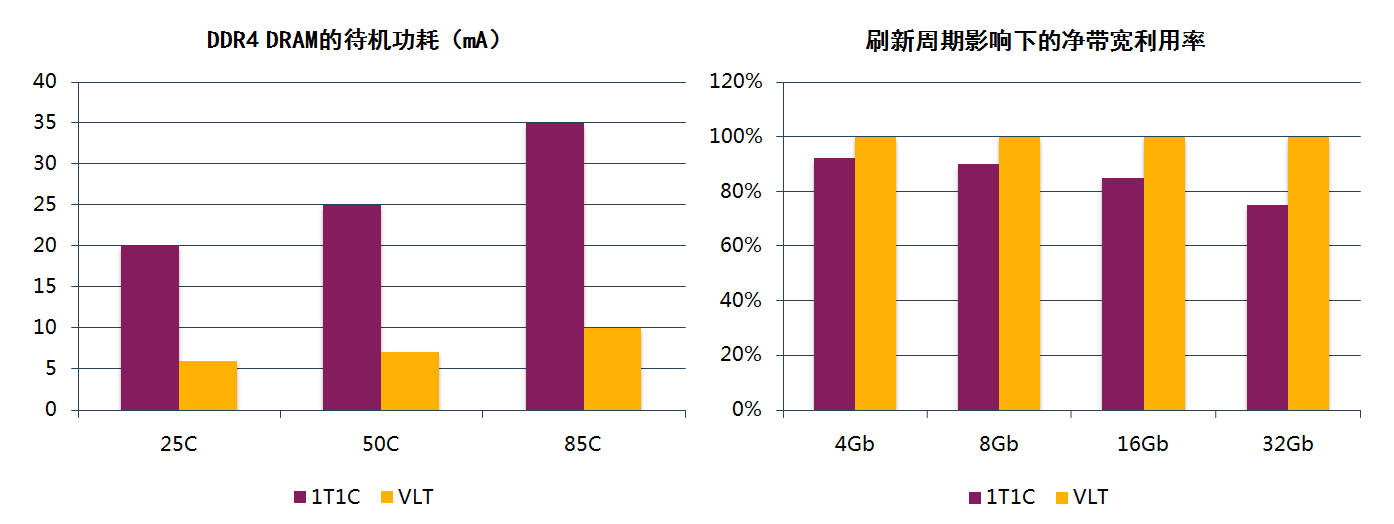

由于没有带漏电的、高功耗的电容结构,因而VLT技术省去了数据刷新并且在120℃高温下仍可以改善功耗,这使得其较适用于工作温度较高的服务器存储器。1T1C和VLT的待机功耗和刷新周期影响下的净带宽利用率对比如图2所示。

图2 1T1C和VLT的待机功耗和刷新周期影响下的净带宽利用率对比图

由于无需新的物理材料,其全部材料是在芯片工厂中已经应用过的,因而模拟软件可以写得很快,这一点与现在市场上的EDA软件有所不同。这也使得其模拟器的速度提升高达1000倍,从而将提前15个月确定出产品的良率及其需要考虑的地方。Charlie Cheng先生称。

据Charlie Cheng先生介绍,VLT的成本很低、制造技术简单,而且无需与电容相关的专利授权是VLT的优势。这项新技术将会首先进入PC和服务器市场。同时,VLT将不会大量授权,预计将只会授权几家公司。

VLT存储单元在2015年已通过验证,目前一款新的完整存储器测试芯片正处于早期测试阶段。Kilopass一直致力于推广这项技术,并正与DRAM制造商进行许可协商。现在已可以向数量有限的特许受让人提供VLT DRAM技术,用于20nm到31nm工艺技术节点。Kilopass已使用其TCAD模拟器,在半导体制造工艺细节上对这两个节点进行了详尽的模拟,新一代10nm技术的验证有望在2017年完成。这也为中国厂商在DRAM市场的发展带来新的机遇。

评论