基于FPGA的多通道高速采样系统设计

摘要:旋转机械的振动监测,对于机械的安全运行和提高设备利用率有重大意义。利用FPGA的并行处理能力,采用高速可编程FPGA模块和嵌入式开发的结合方式,提出了一种基于FPGA的高速、多通道、同步采样实现方法。阐述了对于高速AD芯片的控制,硬件的布局布线,以及对于系统的功能要求,进行了软硬件的设计和调试。通过仿真和实验的结果表明,对于信号发生器发出的高频率正弦波,上位机上能够显示出完好的波形,即基于FPGA的采样设计能够达到多通道,高速采样的要求,可以实现对高速旋转机械振动的实时监测。

0 引言

大型旋转机械包括了汽轮机、水轮机、压气机等机械设备,是航空、电力、机械、石油化工等领域的关键设备。随着工业生产和运行机组的参数不断提高,对设备的可靠性、安全性、经济性提出了更高的要求,促使了对于旋转机械设备振动监测技术的研究。

目前实现数字信号处理主要有两种形式:一种是使用数字信号处理器(DSP),DSP芯片的内部采用程序和数据分开的哈夫结构,而且具有专门的硬件乘法器,可以广泛采用流水线操作,提供特殊的DSP指令,可以用来快速地实现各种数字信号处理算法。然而,由于受到DSP自身性能的限制以及程序指令按顺序执行的特点,难以实现大规模、高速运算;另一种则是现场可编程门阵列(FPGA)。FPGA的结构主要分为三部分:可编程逻辑模块、可编程I/O模块、可编程内部连线,这样就大大降低了印刷电路板设计的工作量和难度,同时,FPGA具有强大的逻辑功能,能对多路信号进行并行处理,可以自定义模块和自定义指令,有效提高了设计的灵活性和效率。因此,在比较低的取样速率时,整体上很复杂的程序可以使用DSP;而在高速,多通道采样方面,FPGA具有明显的优势。实际中,一般的水轮机,汽轮机的旋转速度在每分钟几千转,可以利用DSP完成数据采样,但是遇到超过每分钟万转以上的旋转机械,就可以利用FPGA来完成高速采样。

本设计采用高性能的FPGA芯片EP3C25Q240,高速多通道同步采样AD芯片THS1207,通过良好的PCB布局、模块化编程、多通道并行处理,实现对于高速旋转机械的振动监测与分析。

1 并行系统的工作原理

1.1 系统内部构成

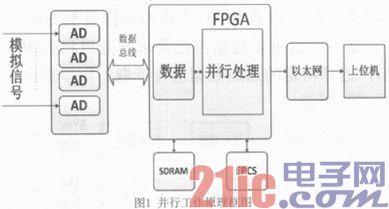

并行系统工作原理框图如图1所示。本系统采用自顶向下的设计方法,可以主要分为AD模块、FPGA控制模块和以太网通信模块。外部振动模拟信号经过信号调制电路后进入AD芯片进行12位模数转换,之后把数字信号并行传递给FPGA芯片。得到采样数据后,FPGA对信号进行并行处理,然后将处理过的数字信号通过以太网完成与上位机的数据通信。

FPGA模块是信号处理系统的核心,它主要完成对数据采集的控制,对数字信号的并行处理与运算以及以太网通信。

1.2 系统外围接口

系统外围主要有AD转换电路、信号调理电路、键相电路、SDRAM和EPCS电路、电源电路、JTAG和AS调试接口、以太网接口和LED显示接口等。

2 板级电路设计

作为控制核心的FPGA芯片采用Altera公司的Cyclone系列的第三代EP3C25Q240,它具有丰富的资源和引脚数量,足够满足本系统需要。凭借其低功耗、高功能、低成本的前所未有的组合,拓宽了大批量、成本敏感的应用。

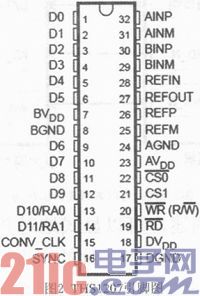

考虑到设计的高速多通道的要求,AD选用了Texas Instruments生产的高速芯片THS1207。THS1207是一个CMOS、低功耗、12位、6 MSPS模拟-数字转换器。对速度、分辨率、带宽和单电源操作都非常适合应用在雷达成像、高速采集和通信。输出误差校正逻辑的多级流水线架构,并提供了在整个工作温度范围内无失码。该THS1207由四个模拟输入,同时进行采样,这些输入可以单独选择,配置为单端或差分输入。为ADC提供1.5~3.5V的内部参考电压。外部也可以参考选择适合ADC精度和温度漂移要求的应用,如图2所示。

D0-D11是并行数据输入/输出口;CS1为芯片的片选信号;RD和WD分别为读写信号;CONV_CLK为提供给AD芯片的工作时钟信号;SYNC为数据同步信号;REFP和REFM为AD的参考电压,可以选择内部或外部参考电压,本设计中采用了内部参考电压;BVDD和DVDD是数字正电源,AVDD是模拟正电源;BGND和DGND是数字地,AGND是模拟地;AINP、AINM、BINP、BINM为模拟信号输入的四个通道。

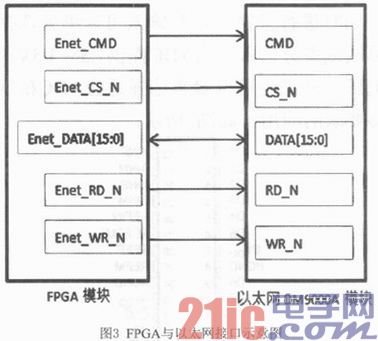

FPGA和上位机的数据通信需要由以太网模块来完成。以太网采用高速DM9000A芯片,该芯片是台湾DAVICOM公司推出的一款高度集成、功能强大、引脚少、性价比高的单片快速以太网控制芯片,非常适用于嵌入式系统设计。DM9000A主要特性是:集成10/100M物理层接口;内部带有16K字节SRAM用作接收发送的FIFO缓存;支持802.3以太网传输协议;体积小,只有48个引脚;功耗非常低,单电源3.3V工作,内置3.3V变2.5V电源电路,I/O端口支持3.3~5.0V的容差。FPGA与以太网的接口示意图如图3所示。

3 多通道并行处理

由于FPGA具有并行处理的优势,在高速多通道同步采样中,更能满足设计的要求。选择硬件描述语言为Verilog,它能够在多种抽象级别对数字逻辑系统进行描述,可以显式地对并发和定时进行建模。本设计是四片AD芯片的同步高速采样,利用FPGA具有的自定义外设以及自定义指令的功能,对于四片AD芯片实现了同步采样的控制,并对数据并行处理。

3.1 单片ADC的控制

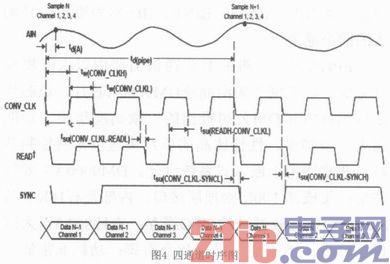

AD芯片THS1207的单通道采样的最大采样速度是6MSPS,四通道采样的最大采样速度是1.5MSPS,本设计采用的是四通道同步采样模式,四通道时序图如图4所示。

在转换过程中ADC有一个自由运行的外部输入时钟CONV CLK。随着每一个CONV CLK信号下降沿,四个通道模拟信号转换后的值提供给相应的读出信号中的数据总线。READ+是,CS1三者的逻辑集成信号,READ+为低电平时表示读有效。信号SYNC是低电平时,第一个通道的数据到数据总线,随后SYNC拉高,第二、三、四通道的数据按顺序依次读取。

3.2 多片AD的同步采样及并行处理

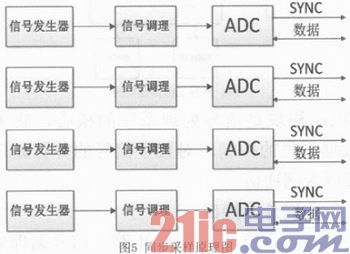

单个AD的控制完成后,就很容易扩展到对四片AD的控制。在采集多通道数据时,需要保持同步采样,本设计采用的方法是每一路信号通过各自的信号调理电路和ADC转换结束后,ADC保持数据,由FPGA依次读取。

在硬件布局时,四片AD共用数据线,读写信号和AD转换时钟信号。因此FPGA通过写命令同时启动这四片AD芯片,十六个通道的模拟信号进入AD。每片AD都有一个数据同步信号SYNC,当判断得到四片AD中的某个SYNC信号是低电平时,则可认为十六道数字信号已同步到位,通过片选信号的切换依次读取各个AD芯片的数据并暂时储存在寄存器中。也可以根据自己需求,开启和关闭某些AD,选择特定的通道数据进行读取。同步采样原理图如图5所示。

3.3 自定义指令

自定义指令是FPGA的嵌入式软核nios ii的一大特色,nios ii有着一个开放式的ALU,用户可以根据自己的要求添加自定义指令来实现应用需求,大大体现了nios ii软核的灵活性。自定义指令的功能是运用Verilog语言,由电路模块来完成的。因此,相比较利用C语言编程来实现功能,自定义指令具有执行速度快的显著特点。Nios ii支持四类自定义指令:组合逻辑指令、多周期用户自定义指令、扩展用户自定义指令、内部寄存器自定义指令来满足各种应用情况。

本设计中旋转机械的振动信号虽然在硬件中经过了信号调理,但是由于元器件间参数的问题,仍旧会存在数据的偏差,运用了自定义指令中的多周期用户自定义指令将数据进行修正。多周期指令需要数据指令和逻辑指令。利用start信号开始执行指令,done信号来表示执行结束,可以返回结果。

同时对于采集得到的数据进行傅里叶变换、滤波等处理,通过自定义指令也能实现,提升了FPGA的信号处理能力。

4 AD时序仿真

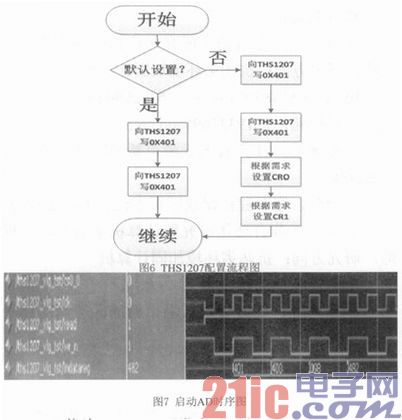

仿真在FPGA的开发中扮演了重要的角色,利用modelsim仿真软件来对编好的AD程序进行时序验证。AD正式工作前,需要通过向AD内部控制寄存器、CR1写命令启动AD,然后才能读取数据。启动AD芯片THS1207的流程图如图6所示,启动AD的仿真结果如图7所示。

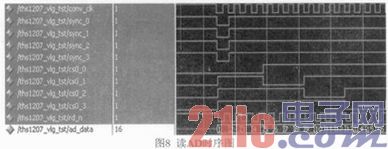

AD芯片THS1207正常启动后就可以开始读取各个通道的数据,由于本设计是十六个通道依次采样,采样结束后,需要通过片选控制信号依次读取各个通道的数据,仿真结果如图8所示。

从仿真结果验证得到编写的AD程序可以完成十六道采样的设计要求。

5 实验结果

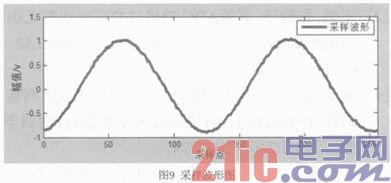

实验采用AD四通道同步采样,利用信号发生器产生正弦波,选择同步采样方式对每个正弦波采样128点,通过以太网传送到上位机,采样得到的波形如图9所示。

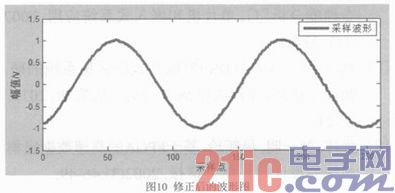

可以利用FPGA的自定义指令,根据需求将得到的数据进行处理,如图10,对得到的波形数据进行偏置为-10和放大倍数为1.05的修正。

实验中当信号发生器发出正弦波的频率达到3000Hz时,即采样频率达到384kHz时,FPGA采集波形能力达到了最大值,相当于180000r /min的旋转机械的基频信号。当超过3000Hz时,采样得到的波形会出现毛刺现象。分析原因,主要是由于nios ii进、出中断服务程序,以及中断服务程序中对采样数据的读取需要花费一定的时间。

6 结束语

本设计利用FPGA并行技术、自定义模块化设计以及nios ii的特色功能即自定制指令,实现了对于旋转机械振动信号的多通道高速同步采样。显示了FPGA可编程、设计灵活、高速的特点,同时也验证了基于FPGA的多通道高速采样系统的可行性。

根据实验结果和理论的最大采样速度还有差距,可以进一步改进系统设计,例如采用DMA优化程序,提高速率。

评论