基于FPGA的视频实时边缘检测系统

摘要:对于视频图像检测与识别的需要,提出了一种基于FPGA的视频边缘检测系统设计方案,并完成系统的硬件设计。通过FPGA控制摄像头进行视频采集,双端口SDRAM对图像数据进行缓存,FPGA再对数据进行实时处理。实际采用DE2-115开发板和CMOS摄像头OV7670为硬件平台进行验证。结果表明,该系统具有实时性高,检测准确的特点,达到了设计要求。

本文引用地址:https://www.eepw.com.cn/article/201610/308525.htm随着科技的发展,视频采集系统越来越广泛的应用于各个领域,如体育直播,视频会议,导弹的电视制导等等。而图像边缘是图像的基本特征之一,其中包含了很重要的边界信息,这些信息是图像分析、目标识别的基础。在交通信息控制应用领域中,边缘检测已经是车牌识别、车流量监控、自动导航等技术中的重要环节。通过有效的边缘检测,可以大大简化后续图像处理过程对图像信息的分析工作。对于视频图像的边缘检测,若采用软件方式实现由于受到系统处理速度的限制,容易出现断帧现象,这对于要求实时处理的情况下将是一个很大的缺陷。硬件实现主要有基于专用芯片,基于DSP和基于FPGA的3种处理方式。基于专用芯片方式并不适合前期产品的开发。基于DSP方式在运算速度、数据吞吐量等方面有限制。本设计基于FPGA实现,边缘检测采用流水线结构。实验结果表明,该系统十分适合视频数据的处理。

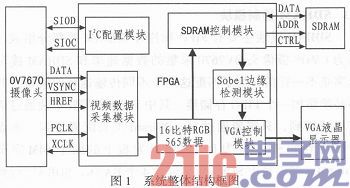

1 系统总体设计

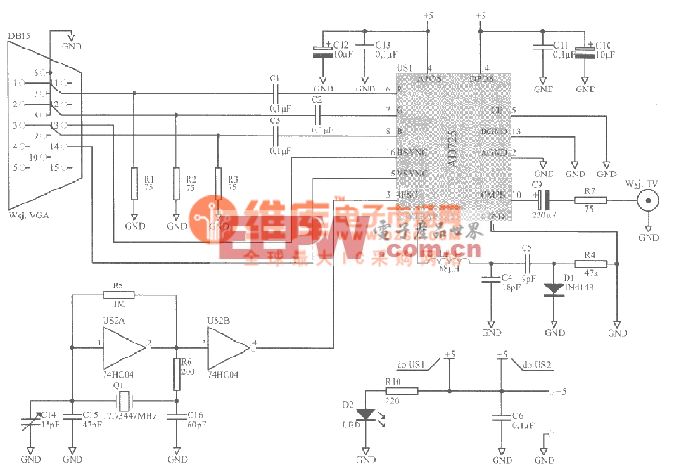

本系统基于一片Altera公司的Cyclone IV系列的EP4CE115F29CN7主控FPGA,系统的整体结构框图如图1所示。主要包括:摄像头I2C配置模块、视频数据采集模块、SDRAM控制模块、Sobel边缘检测模块和VGA控制模块。FPGA首先通过I2C总线完成对OV7670的初始化,然后将采集到的数据通过视频数据采集模块转换成RGB565标准的视频数据,图像数据通过FIFO_IN模块在SDRAM中进行缓冲,Sobel边缘检测模块通过FIFO _OUT模块读取数据并进行处理,VGA控制模块控制VGA接口的行同步和场同步信号完成VGA显示。

2 视频采集与边缘检测子模块

2.1 I2C配置模块

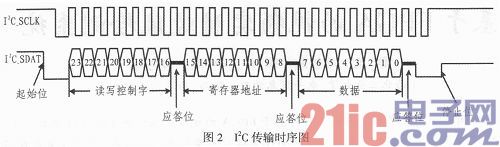

本系统采用OmniVision公司的OV7670这一款CMOS传感器,为系统提供视频信号。通过SCCB(Serial Camera Control Bus)总线对OV7670的共201个控制寄存器进行配置,来改变输出数据的格式、视频分辨率、传输方式,调整图像的白平衡、饱和度、色度、伽玛曲线等。两线制的SCCB总线与I2C总线相同,都是双向两线制同步串行总线。I2C传输时序如图2所示,I2C_SCLK就等同于SCCB中的SIOC、I2C_SDAT就等同于SC CB中的SIOD,模块每次传输24位数据,前8位为从设备地址(0x42代表写寄存器,0x43代表度寄存器),中间8位是从设备寄存器地址,最后8位是对寄存器进行配置的数据。

2.2 视频数据采集模块

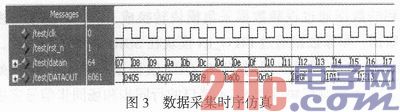

视频数据采集模块,主要是通过FPGA配合CMOS摄像头OV7670的行、场同步信号采集图像数据。首先通过配置控制寄存器,控制OV7670输出视频数据为RGB565格式。因为OV7670数据位宽为8,视频数据采集模块主要是将采集到的前后2个8位数据合并成一个16位数据,以方便数据在SDRAM中的缓存以及后续模块的处理。如图3所示为数据采集ModelSim时序仿真图。

2.3 SDRAM控制模块

SDRAM模块主要有FIFO和片外SDRAM两部分组成,因为CMOS摄像头OV7670采集的数据速率和SDRAM读写速率是不一样的,为了匹配这两个不同传输速率的模块,其中必须添加一个FIFO存储器。其中FIFO不需要单独通过语言描述得到,只需要通过MegaWizard工具配置得到。本设计中用到的SDRAM为DE2-115开发板上的两个64M字节SDRAM,其中每个SDRAM又包含4个BANK。SDRAM行地址线和列地址线是复用13位的地址总线,在读写时,先要激活某个BANK,接着锁存行地址,最后在读写指令有效时锁存列地址。SDRAM的最高读写速率可达到166 MHz,本系统中应用为100 MHz,同时每个时钟上升沿又可读写16 bit数据,因此SDRAM完全可以实现数据的无缝缓冲工作。

2.4 Sobel边缘检测模块

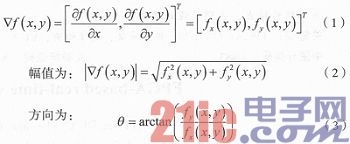

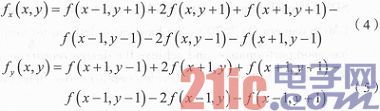

图像边缘是一幅图像中灰度变化比较剧烈的区域,计算灰度图像中各区域的梯度幅值可以用来判定图像的边缘信息。设图像的亮度为f(x,y),则梯度可以定义如下:

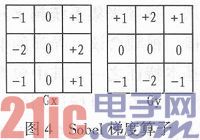

Sobel边缘检测便是是基于梯度的检测,其利用Sobel算子如图4所示Gx与Gy,在3×3的图像邻域内和亮度数据做卷积运算,表达式如下:

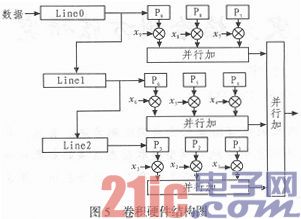

用硬件左边缘检测,由于是实时处理,SDRAM中缓存的数据只是连续视频图像中一帧图像,而且视频数据还不停的从摄像头中传过来,因此就不能像软件处理那样先建立一个二维的数据阵列,这样就必须采用流水线方式进行运算,流水线数目和每次参加运算的像素数目相等,这里就总共需要9条流水线。为此我们就专门设计了3条Line_Buffer来完成式(4)与式(5)的运算,3条Line_Buffer由MegaWizard中配置的alts hift_tab完成,altshift_tab实际上就是一个移位寄存器,因为视频分辨率为640×480像素,所以每条Line_Buffer实际是向后移位一整行,也就是640个像素值。这样就等同于3条Line_Buffer中的数据视频图像中相毗邻的三行图像数据,这3行数据再与Sobel算子做卷积。如图5所示为卷积运算硬件结构图,其中P9—P1为像素数据,X9--X1为Sobel梯度算子。乘法与并行加法部分分别有MegaWizard配置的altmult_add和parallel_add完成。

2.5 VGA显示模块

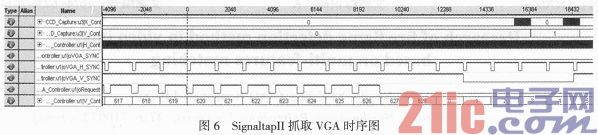

VGA显示器的显示采用逐行扫描,从屏幕左上方开始,从左到右,从上到下扫描。每一行的现实受到行同步信号(HREF)控制,每一帧的信号受到场同步信号(VSYNC)控制。本系统中CMOS摄像头采集图像分辨率为640×480像素,VGA(640×480)的工业标准为行扫描:Ta(同步脉冲)=96,Tb(行消隐后肩)=40,Tc=8,Td(有效时序)=640,Te=80,Tf(行消隐前肩)=8,Tg(行周期)=800;场扫描:Ta(同步脉冲)=2,Tb(场消隐后肩)=25,Tc=8,Td(有效时序)=480,Te=8,Tf(场消隐前肩)=2,Tg(场周期)=525。图6为由SignalTapII抓取的VGA时序图,其中最后一行数据为当前一帧视频所显示的行数统计。

3 实验结果

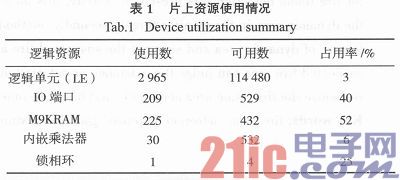

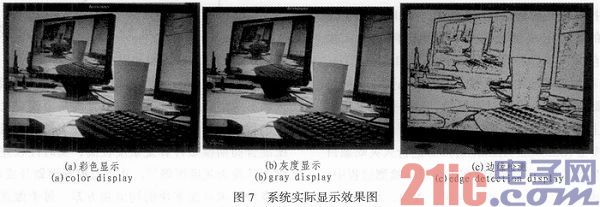

由QuartusII软件综合仿真后可知,系统最高工作频率为100MHz,片上资源使用情况如表1所示。通过DE2-115开发板为验证平台,对上述系统进行测验,结果如图7所示。其中,图7(a)为对所采集到的视频直接通过液晶显示器显示的彩色图像,图7(b)为对采集的视频进行处理得到的灰度图像,图7(c)灰度图像经过Sobel边缘检测算法处理后的图像。实际液晶显示彩色图像、灰度图像、边缘检测图像完整顺畅,并没有断祯现象发生。

4 结论

设计了一个基于FPGA的的视频实时边缘检测系统,利用FPGA良好的并行结构,使计算速率得到了很大提升,达到了系统的实时性要求。实现了VGA分辨率视频在液晶屏上的彩色显示、灰度显示、边缘检测图像显示,在图像纹理复杂的情况下也能较好的提取图像边缘。实验结果表明,该系统具有速度快、精度高等优点,能够很好的应用在目标识别、目标跟踪、智能视频监控等领域。

评论