基于FPGA的数字存储示波器对外围芯片的控制设计

数字存储示波器作为测试技术的重要工具,被广泛应用于各个领域,并逐步取代传统模拟示波器。其采样数据是波形运算和分析的基础,直接影响到整个数字存储示波器的准确性。从这点出来,提出采用现场可编程逻辑器件( FPGA) 作为数字存储示波器采样控制系统的核心,从芯片间有效协助的角度,基于FPGA 设计ARM 接口通信控制模块和外围芯片驱动功能模块,以FPGA 为核心有效地组织其它芯片,共同完成数字存储示波器数据采样过程,确保数据按需求采样,有效地提高数字存储示波器的采样效率和数据的可靠性。

本文引用地址:https://www.eepw.com.cn/article/201610/308397.htm1 数字存储示波器的总体设计方案

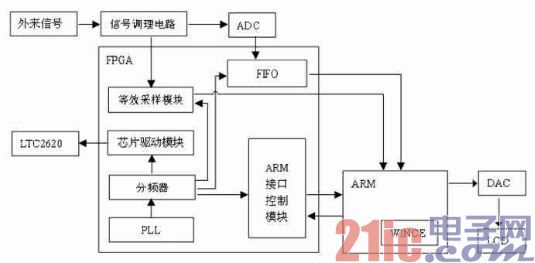

数字存储示波采用双处理器( ARM + FPGA) 的嵌入式系统设计方案,ARM 内嵌WINCE 操作系统,整个采样系统主要在FPGA 里完成,从功能的角度分成采样信息处理子系统与采样控制子系统,本文着重介绍采样控制子系统的驱动部分,由ARM 接口控制模块与芯片驱动模块组成。如图1 所示:

图1 数字存储示波器总体功能模块图

2 系统驱动模块设计

2. 1 ARM 接口通信控制模块设计

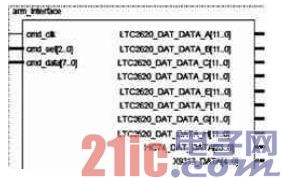

ARM 接口通信控制模块为主要的控制模块,如图2 所示。

图2 ARM 接口通信控制部分功能模块图

加入这个模块而不直接链接两个芯片有以下两点原因:

1) ARM 作为主控芯片的控制模块,引脚数量有限。如果ARM 接口直接与FPGA 接口相连,会占用ARM 过多的接口。

2) ARM 和FPGA 相连的信号线由于存在各种干扰,有时会出现毛刺现象,影响测量效果。

所以为了测量的稳定准确,需要加入FPGA 和ARM 的接口模块。此模块是本设计的重点也是难点。其原理以下结合图2 来说明。

ARM 接口通信控制模块左边为跟ARM 链接的接口,分别为1 路时钟cmd_clk,3 路的命令线cmd_sel[2. . 0],8 路数据线cmd_data[7. . 0]。右边为FPGA 响应的相关接口,在此不作一一讲述,下面主要讲术FPGA 与ARM 之间的通信协议。

cmd_clk 为1 位输出接口,是ARM 与FPGA 的同步时钟,用作同步通信。

cmd_sel[2. . 0]为3 位输出接口,用作设置cmd_data[7. . 0]的模式选择。

cmd_data[7. . 0]为8 位输出接口,是ARM 发送到FPGA 的命令或数据。

功能实现方面采用了VHDL 语言,以文本输入作为设计输入,主要运用CASE 与PROCESS 语句,部分程序如下所示。

PROCESS( cmd_clk, cmd_sel) / /进程,对cmd_clk 与cmd_sel 进行变化捕捉。

BEGIN / /进程开始。

IF cmd_clk'EVENT AND cmd_clk = '1' THEN / /捕捉时钟信号上升沿触发。

IF cmd_sel( 2) = '1' THEN / / cmd_sel( 2) = '1'时, cmd_data[7. . 0]的输出为数据模式

r_add_add = cmd_data; / /数据赋值

ELSE / / cmd_sel( 2) = '0'时, cmd_data[7. . 0]的输出为命令模式

CASE r_add_add IS / /命令查询

WHEN X00 = > IF cmd_sel = 000 THEN r_DAT_DATA_A( 7 DOWNTO 0) = cmd_data; - -

ELSIF cmd_sel = 001 THEN r_DAT_DATA_A( 11 DOWNTO 8) = cmd_data( 3 DOWNTO 0) ;

END IF;

WHEN X01 = > IF cmd_sel = 000 THEN r_DAT_DATA_B( 7 DOWNTO 0) = cmd_data;

ELSIF cmd_sel = 001 THEN r_DAT_DATA_B( 11 DOWNTO 8) = cmd_data( 3 DOWNTO 0) ; END IF;

WHEN X02 = > IF cmd_sel = 000 THEN r_DAT_DATA_C( 7 DOWNTO 0) = cmd_data;

ELSIF cmd_sel = 001 THEN r_DAT_DATA_C( 11 DOWNTO 8) = cmd_data( 3 DOWNTO 0) ; END IF;

WHEN X03 = > IF cmd_sel = 000 THEN r_DAT_DATA_D( 7 DOWNTO 0) = cmd_data;

ELSIF cmd_sel = 001 THEN r_DAT_DATA_D( 11 DOWNTO 8) = cmd_data( 3 DOWNTO 0) ; END IF;

……/ /省略

WHEN X08 = > IF cmd_sel = 000 THEN r_HC74_DAT_DATA( 7 DOWNTO 0) = cmd_data; - -

ELSIF cmd_sel = 001 THEN r_HC74_DAT_DATA( 15 DOWNTO 8) = cmd_data; - -

ELSIF cmd_sel = 010 THEN r_HC74_DAT_DATA( 23 DOWNTO 16) = cmd_data; END IF;

/ / cmd_sel[2. . 0]的后两位作为数据位数的选择,这里可选为8 位、16 位、24 位。

……/ /省略

WHEN OTHERS = > r_X9313_DATA = cmd_data( 4 DOWNTO 0) ;

END CASE;

END IF;

END IF;

END PROCESS;

本程序是一个进程,当cmd_sel( 2) = '1'时,cmd_data[7. . 0]作为数据传输。当cmd_sel( 2) = '0'时,cmd_data[7. . 0]作为命令选择传输。cmd_sel( 1) 与cmd_sel( 0) ,作为发送数据位数选择,这是由于不同的指令操作,需要不同的数据位数,在这段程序中,有需要发送8 位数据的,有需要发送12 位的数据,有需要发送16 位的数据,还有需要发送24 位的数据,这取决于驱动的芯片所固定的数据位输入格式要求。

2. 2 芯片驱动模块设计

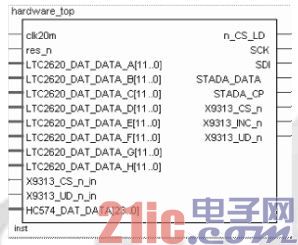

芯片驱动模块的例化组件图,如图3 所示。

图3 芯片驱动模块例化组件

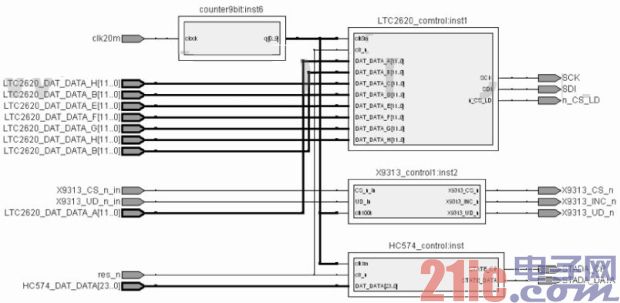

图3 是已经封装好的功能模块,其内部结构如图4 所示。

图4 LTC2620 的接口例化组件图

由此可知,该模块内部还可以有子模块。分别为控制外围三个芯片的驱动,它们是芯片LTC2620、芯片X9313、芯片HC574。这些子模块只是一个接口,并非是一个真正的芯片,可以说是一个接口函数以图形化的方式来给调用,让程序结构更佳形象具体,其实它们都是通过VHDL 语言编程程序代码而成的。图4 的左边是输入接口,主要是与ARM 接口通信控制模块( 图2) 的接口连接,而右边的是输出接口,当然这些输出接口是FPGA 的I /O 引脚,这才能与真实的芯片相应应的引脚连接。

下面以芯片LTC2620 为例,说明其驱动过程。图4 右上角是LTC2620 的接口例化组件,是由VHDL语言生成的,首先是VHDL 的实体部分,主要是定义端口及其属性。

ENTITY LTC2620_comtrol IS

PORT(

clk5m : IN STD_LOGIC;

clr_n : IN STD_LOGIC;

DAT_DATA_A : IN STD_LOGIC_VECTOR( 11 DOWNTO 0) ;

DAT_DATA_B : IN STD_LOGIC_VECTOR( 11 DOWNTO 0) ;

DAT_DATA_C : IN STD_LOGIC_VECTOR( 11 DOWNTO 0) ;

DAT_DATA_D : IN STD_LOGIC_VECTOR( 11 DOWNTO 0) ;

DAT_DATA_E : IN STD_LOGIC_VECTOR( 11 DOWNTO 0) ;

DAT_DATA_F : IN STD_LOGIC_VECTOR( 11 DOWNTO 0) ;

DAT_DATA_G : IN STD_LOGIC_VECTOR( 11 DOWNTO 0) ;

DAT_DATA_H : IN STD_LOGIC_VECTOR( 11 DOWNTO 0) ;

n_CS_LD : OUT STD_LOGIC;

SCK : OUT STD_LOGIC;

SDI : OUT STD_LOGIC) ;

END;

其中n_CS_LD、SCK、SDI 为输出端口,是根据芯片LTC2620 的输入引脚而设定的。芯片LTC2620 引脚图如图5 所示。

图5 LTC2620 引脚图

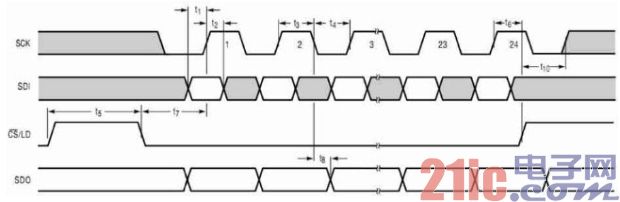

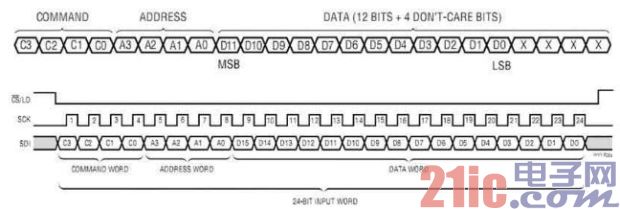

接口与引脚已经连接好,但还需要仿真这三个引脚的工作时序。这就需要根据芯片LTC2620 手册说明来来模拟其时序以及其数据输入格式,为4 位命令+ 4 位地址+ 12 位数据流,共20 位数据,但数据一般以8 位为单位,即一个字节,所以需要发送24 位数据,其中16 位数据流的前4 位都需要作置零处理。LTC2620 时序图如图6 所示。

图6 LTC2620 输入引脚时序图

数据输入格式如图7 所示。

图7 输入引脚数据格式图

接着,使用VHDL 在其结构体部分编写LTC2620 时序,需要设计两个进程来完成,分别是PROCESS( clk5m,clr_n) 进程和PROCESS( load_clk,clr_n,DAT_DATA_A) 进程。

首先定义数据格式,分成三部分,COMMAND( C3 - C0) 、ADDRESS ( A3 - A0) 和DATA ( D11 -D0) ,一共为20 位,要分三个字节发送,即24 位。数据格式定义的VHDL 代码:

CONSTANT CNT_COMMAMD_DATA : STD_LOGIC_VECTOR( 3 DOWNTO 0) : = 0011 ;

/ /COMMAND( C3 - C0)

SIGNAL ADDRESS_DATA : STD_LOGIC_VECTOR( 3 DOWNTO 0) ;

/ / ADDRESS( A3 - A0)

SIGNAL DAT_DATA: STD_LOGIC_VECTOR( 11 DOWNTO 0) ;

/ / DATA( D11 - D0)

根据图6,对时序SCK、SDI、CS /LD 进行定义:

SIGNAL r_n_CS_LD,r_SCK,r_SDI : STD_LOGIC;

内部时钟定义:

SIGNAL r_load, load_clk, load_en : STD_LOGIC;

再设定三个进程来模拟图7 的SCK、SDI、CS /LD 三个时序图。

1) 进程1 主要是通过内部时钟生成SCK 时序

代码为:

PROCESS( clk5m, clr_n)

VARIABLE tp : INTEGER RANGE 0 TO 25;

BEGIN

IF clr_n = '0' THEN

tp: = 0; load_clk = '0';

ELSIF clk5m'EVENT AND clk5m = '1' THEN

IF tp 25 THEN

tp: = tp + 1; load_clk = '1';

ELSE

tp: = 0; load_clk = '0';

END IF;

END IF;

END PROCESS;

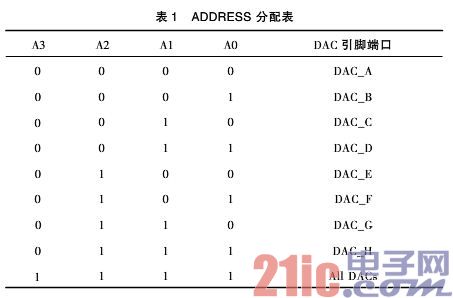

2) 进程2 主要是设置LTC2620 的8 个输出引脚VoutA - VoutH 与ADDRESS ( A3 - A0) 之间的对应关系,ADDRESS,如表1 所示。

使用CASE 语句完成,代码如下:

CASE state IS

WHEN 1 = > DAT_DATA = DAT_DATA_B; ADDRESS_DATA = 0001 ;

WHEN 2 = > DAT_DATA = DAT_DATA_C; ADDRESS_DATA = 0010 ;

WHEN 3 = > DAT_DATA = DAT_DATA_D; ADDRESS_DATA = 0011 ; WHEN 4 = > DAT_DATA

= DAT_DATA_E; ADDRESS_DATA = 0100 ; WHEN 5 = > DAT_DATA = DAT_DATA_F; ADDRESS_DATA

= 0101 ; WHEN 6 = > DAT_DATA = DAT_DATA_G; ADDRESS_DATA = 0110 ; WHEN 7 = > DAT_DATA

= DAT_DATA_H; ADDRESS_DATA = 0111 ; WHEN OTHERS = > DAT_DATA = DAT_DATA_B; ADDRESS_

DATA = 0001 ; load_en = '0';

END CASE;

3) 进程3 主要是设置DATA ( D11 - D0) 的数据输出,每次需发送24 位数据,其中4 位无用上,给置0 处理,代码如下:

IF r_load = '0' THEN

data( 23 DOWNTO 20) : = CNT_COMMAMD_DATA;

data( 19 DOWNTO 16) : = ADDRESS_DATA;

data( 15 DOWNTO 4 ) : = DAT_DATA;

data( 3 downto 0) : = 0000 ;

……/ /省略;

end IF;

3 结语

本文详细介绍了使用VHDL 硬件描述语言,程序编写过程,对两个功能模块进行基于FPGA 的嵌入式系统程序开发。实现了ARM 接口通信控制模块、芯片驱动模块的程序设计,有效地解决了芯片间之间的通信与驱动的问题,以FPGA 为核心,有效地实现芯片间的相互协作,为数字存储示波器数据采样提供重要的可靠性。

评论