基于DSP和FPGA的水声定位系统主控机设计

近年来,海洋开发日益影响人们的生活和国家社会的发展。海洋油气开发、海底光缆工程、海底矿产资源探测等等都离不开水下声学定位的支持。目前广泛采用的水下目标定向系统是合作目标定向系统,合作目标定向系统可分为合作目标、声传感器阵列、信号处理和数据处理等部分。合作目标即是被测量的目标,但它能发射用于测量的合作信号。声传感器阵列在空间布设成一定的几何形状,对合作信号进行取样,获得目标的原始数据。信号处理部分把接收到的采样信号,转变成能反映目标声场特征的有用信号,形成观测数据。上述系统中信号处理和数据处理部分是定位系统的核心部分,本文提出一种水下合作目标定向系统的数字信号处理硬件平台解决方案以及基于该平台的声学定位算法的硬件实现方案,该平台采用FPGA和DSP为主要芯片,具有体积小、实时性强等特点。

本文引用地址:https://www.eepw.com.cn/article/201610/308370.htm1 硬件总体设计方案

1.1 硬件工作原理

该数字信号处理硬件平台应用于水下应答器的定位系统中,具有4路模拟信号输入和1路模拟信号输出。系统工作时,主控机获得通过网络接口获得上位机(PC)一组命令输出一组经过编码的模拟信号,相应的应答器发送一组固定频率脉冲信号,主控机通过计算四元十字阵接收到的4路模拟信号可以得到应答器的方位距离信息,同时主控机通过RS232接口和舰载MCU通信获得GPS数据、运动参考单元等信息。主控机最后将计算得出的信息及串口接收到的信息传给上位机。

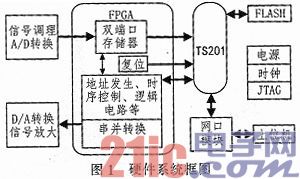

1.2 硬件框图

系统硬件框图如图1所示。根据水下应答器定位的处理任务及实时性要求,选用美国亚德诺半导体技术有限公司(Analog Device Inc,ADI)的TigerSHARC系列ADSPTS201作为主处理器。它能够对4路A/D同步采集的模拟信号进行有限冲击响应(Finite Impulse Response,FIR)滤波、副本相关、快速傅里叶变换等运算,检测出有用信号,精确估计信号时延并得出应答器方位距离信息,最终将计算结果通过网络接口上传给上位机,实现目标的定位。

2 DSP系统设计

2.1 高速信号处理器ADSPTS201芯片简介

ADSPTS201 TigerSHARC DSP是一款性能极高的静态超标量处理器,其内核工作频率高达600 MHz,具有24 Mbit的片内存储,专对大的信号处理任务和通信结构进行优化。一

个指令周期仅需1.6 ns,且DSP每周期能够执行多达4条指令,24个16位定点运算和6个浮点运算。4条相互独立的128位宽度的内部数据总线,每条总线分别连接6个4 Mbit内部存储器块中的1个,提供四字的数据、指令及I/O访问和33.6 GB/s的内部存储器宽度。

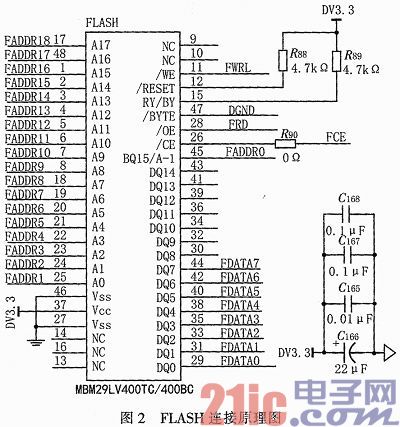

2.2 FLASH接口电路设计

ADSP TS20X系列处理器支持多种程序引导加载方式:1)EPROM引导方式通过处理器外部总线进行程序引导和加载:2)主机引导方式通过主机或者将其他处理器作为主机,实现处理器的程序引导和加载;3)链路口引导方式通过处理器的链路口实现程序的引导和加载;4)非引导方式通过外部不同的Strap信号,从内部存储器的不同地址开始执行程序。

本系统采用第一种引导方式,外部存储器选择富士通公司的FLASH器件MBM29LV400TC,连接方式如图2所示。

ADSPTS201的FLASH加载方式比较容易实现。在DSP复位期间,通过确实引脚BMS信号,确认FLASH加载方式。ADSPTS201对FLASH的少些也比较容易实现,硬件配置好之后只要将加载程序通过编译生成的.ldr文件通过外部总线写入外部存入空间中即可。

2.3 网络接口电路设计

系统与上位机PC的交流是通过网口的方式实现,本系统的网口采用DSP直接控制,网口芯片选用W5300。W5300是WIZnet公司的单芯片器件,采用0.18μmCMOS工艺,内部集成10/100M以太网控制器、MAC层协议和TCP/IP协议栈,主要应用于高集成、高稳定、高性能和低成本的嵌入式系统中。

本系统中采用TCP的方式进行通信,在通信前进行握手保证下发的命令和上传的数据能够实时的传送。上位机向下发送命令和参数时,因为可以采用中断的方式进行,可以有

效的节约可编程输入输出口FLAG口(ADSPTS201只有4个FLAG口FLAG0—FLAG3)。

2.4 电源设计

ADSPTS201处理器要求有多个电源:VDD(内部)、VDD_A(模拟PLL)、VDD_IO(外部IO)以及VDD_DRAM。其中对电源VDD滤波可以得到VDD_A。因为本系统选用时钟频率是600MHz,所以需要3种电压值,分别是:1.2 V(典型电流2.9 A)、1.6 V(最大电流0.43 A)、2.5 V(典型电流0.15 A)。

系统输入电压是5 V,考虑到1.2 V需要的电流较大(FPGA的内核电压也是1.2 V),为了减少电源复杂度,采用一个DC/DC器件单独供电,这里选用TI公司的TPS54612器件,输入电压是3~6 V,输出电流可达到6 A,满足系统要求。对于1.6 V和2.5 V,电流要求比较低,分别选用TI公司TPS55386和TPS72516器件,可以满足系统要求。

另外,因为ADSPTS201的内核电压1.2 V的工作电流较大,达到了3 A,为了保证处理器能够正常工作,必须给TS201安装散热装置如散热片等。

3 FPGA系统设计

由于ADSPTS201处理器的偏重于信号处理,控制能力较弱,所以本系统FPGA基本完成了所有逻辑控制、外部接口、外部通信的功能。而对于FPGA而言,这些工作都能够轻松胜任,同时也能够让DSP专注于信号处理任务本系统选择的是Altera公司的CycloneⅢ系列FPGA。

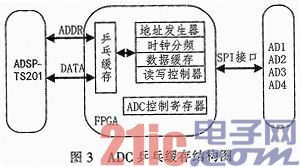

3.1 ADC模块设计

本系统的AD转换接口采用ADI公司AD7985芯片,采样频率可达到2.5 Msps,采样精度即数据位数为16 bit,采用的SPI接口。

FPGA中,首先将AD采集到的串行数据转换成并行数据存入双口RAM,当双口RAM半满和全满时分别发送一次IRQ0中断,完成一次乒乓缓存,保证了ADC能够一直保持采集状态的同时处理器能够有足够时间进行数据的处理,使系统具有实时性。同时ADC控制器寄存器映射到DSP某一地址上,启动/停止AD转换,其系统框图如图3所示。

3.2 DAC模块设计

本系统的DAC器件选用的ADI公司的AD5664,采用SPI接口,串行时钟可以达到70 MHz,精度是16 bit。

FPGA中的DAC逻辑接口的主要功能是将DSP写入FPGA的发射信号的组号信息,然后通过查表得到写入DAC寄存器的16位并行数据,保证DAC器件通过D/A转换产生所需组号对应的信号。

3.3 PGA放大模块设计

数字量控制增益的放大器也比较多,但是带宽及增益能够满足的要求比较少,单片增益无法达到60 dB,因此需要两片可编程增益放大器级联以实现60 dB的可变增益。选择可编程增益放大器还必须考虑前级滤波器输出为双极性信号,而后级的ADC要求为单极性输入。因此综合考虑,选择PCA113和PGA103级联,实现系统的可变增益要求。

PGA103是通用型可编程增益放大器,由两个CMOS/TTL兼容的输入进行数字编程选择,增益为1、10或100。PGA113可提供1、2、5、10、20、50、100以及200等范围增益,采用SPI写入命令字控制。

FPGA中放大增益的控制采用AGC的方式,首先设置一个默认倍数,将ADC采集的数据存入DSP,计算其信号的能量,通过对比实验室数据,DSP将需要的倍数写入FPGA建立的相应的寄存器,最后通过SPI接口和控制线写入PGA113和PGA103,实现可编程放大的功能。

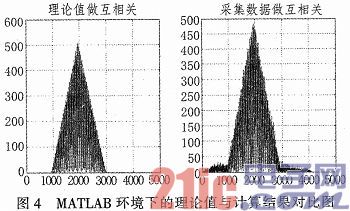

4 系统验证与结论

将本系统和应答器合作,在消声水池进行试验,将TS201处理器计算所得到的数据与MATLAB环境下的计算结果进行对比,如图4所示,可看出理论的互相关峰值和计算得出的互相关峰值是一致的,证明该计算结果的准确性。

5 结束语

文中阐述了基于DSP+PGA的水声定位系统主控机设计,并且实现了产生不同组号发射信号以及对4路接收通道信号的计算,成功的计算出了合作目标的方位信息,具有实际的工程价值。

评论