高速公路宏观动态交通流模型的FPGA仿真实现

高速公路宏观动态交通流模型以交通流的集总行为为研究对象,描述了交通流的空间分布及随时间变化的规律,能较精确地描述高速公路交通流的真实行为,不仅是交通自动控制系统设计、分析、仿真决策的基础,也是交通预报和评价某些交通设施设计所需要的。其中,希腊学者Markos Papageorgiou所提出的Papageorgiou模型,能够以较小的计算量和满意的精度描述车道数目单一、出入匝道无特大流量冲击的高速公路交通状况而广泛应用。

本文引用地址:https://www.eepw.com.cn/article/201610/308310.htm对交通流模型进行在线仿真,或验证某算法对实际道路的控制效果时,有时由于交通数据庞大或控制算法过于复杂,往往消耗大量机时。尤其在外场环境下操作,工控机不仅体积、功耗庞大,还易出现工作失常的现象,在交通控制的实际应用中表现欠佳。FPGA技术高速、低成本、小型化的优势使其理论研究与实际应用成为炙手可热的研究课题,目前已经完全具备数据运算、信息处理、滤波计算等功能,常常使一些原来比较难解决的技术瓶颈得以轻松实现,从而使产品的可移植性增强,开发周期大为缩短,性价比大幅提高,同时FPGA可以实现纯硬件浮点运算功能,克服定点数据对高精度、数据范围较大的运算无能为力的缺陷,更适合科学与工程计算。因此本文采用浮点数在FPGA上实现Papa georgiou模型的仿真。

1 高速公路交通流宏观动态模型

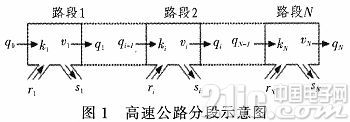

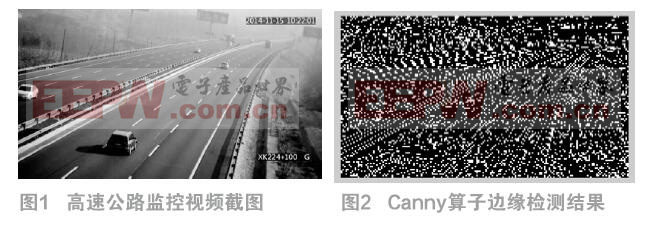

宏观动态交通流模型又称为交通流连续介质模型,它通过对单向运动的交通流在某时刻t在某一位置x的有关变量来把握交通的本质。各研究组织所提出多种形式交通流模型,其间主要差别在于交通流量、车辆平均速度和车流密度的关系的表征,以及上下游交通相互作用的描述形式。为了简化模型使其便于应用在实际中,通常根据高速公路几何形状和交通状态将其划分成若干路段,路段可不等距划分,但应保证每段路段车道数目相同,至多有一个入口、一个出口,每个路段的几何形状大致相似,每个路段内的交通状态近似均一,Papageorgiou模型也采用如图1所示的分段方式:

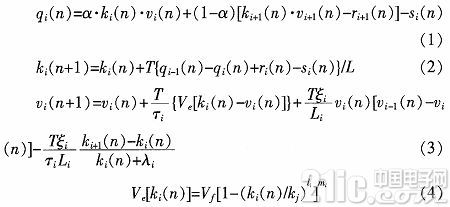

基于上述高速公路的分段方式,其数学表达式如式(1)~(4)所示:

式(1)~(4)分别是动态流量模型、动态交通流密度模型、动态速度模型和速一密关系模型,各符号含义见文献。上述模型涉及到了加减乘除及幂运算,目前Quartus II中有公开的浮点数运算IP核可实现加减乘除运算,但式(4)中出现有底数、指数可能均为浮点数的幂运算。本文根据所选参数进行多项式拟合,将所有运算均限定在加减乘除的浮点数运算范围内。

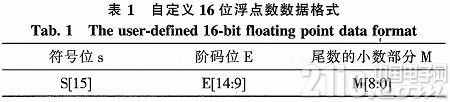

2 16位自定义浮点数数据格式

Quartus II软件自带的IP核的输入输出数据采用IEEE754单精度32位浮点数格式,其数据结构表示如下:

其中S为1位符号位,E为8位阶码位,M为尾数的24位小数位。调用QuartusII浮点数运算IP核实现加减乘除的操作,其资源消耗依次为加减运算消耗LE单元个数均为1 497,消耗嵌入式乘法器个数均为0:乘除运算消耗LE单元个数分别为809、3345,消耗嵌入式乘法器个数分别为0、7。对一个路段进行仿真时,至少需要6次加法、7次减法、12次乘法、4次除法,仅实现加减乘除运算所消耗FPGA逻辑资源已蔚为壮观,若要仿真多个路段,将付出巨大的硬件成本,甚至无法实现,因此本文在IEEE754浮点数格式的基础上采用自定义16位浮点数格式,编写浮点运算模块,尽量减少FPGA资源的消耗,其数据结构为:

其中S为1位符号位,E为6位阶码位,M为尾数的9位小数位,隐藏整数位1,其表示的数据值下式所示:

上式中,当S为0时,A为正数,当S为1时,A为负数;E-31为浮点数的指数,指数可在2-31到231之间变化;尾数采用原码表示,整数部分1为缺省值,不在上述格式中表示;0在上述格式中,阶码和尾数均为0,符号位可以是任意值。为方便说明自定义浮点数的运算过程,设有两个浮点数是a和b,其数据格式如式(6)所示。

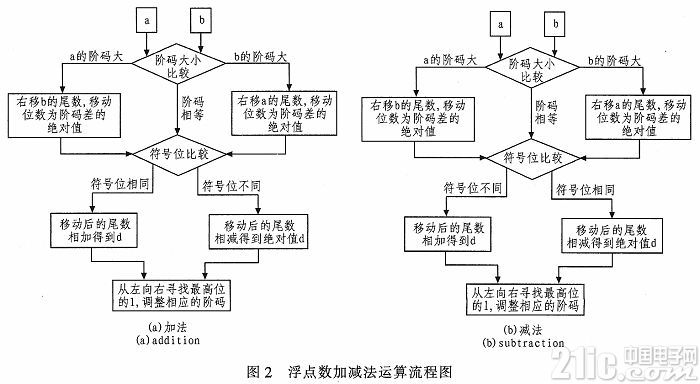

2.1 自定义16位浮点数加法和减法运算

浮点数加、减法的操作过程相似,流程图如图2所示。

1)对阶操作:在两数尾数的小数部分的高位补1,比较两数的阶码是否相同。若相同,直接进入第2)步;若不同,比较两个数的阶码大小,令阶码小的尾数连同高位补的1向右移位,右移的尾数等于阶差的绝对值;

2)符号位操作:加法运算,若两数符号相同,则符号位同两加数;若两加数符号相异,符号位由绝对值较大的加数决定。减法运算,被减数和减数的符号相异,则两数的绝对值相加;两数符号相同,则两数相减再取绝对值。结果的符号位取被减数的符号位(当被减数的绝对值较大时)或者是减数的符号位取反(当减数的绝对值较大时);

3)归一化操作:若步骤1)和2)所得结果为非规格化数,找出运算结果的最高位1,由高至低依次将其后部分存入最终结果,阶码做相应的调整。

2.2 自定义16位浮点数乘法和除法运算

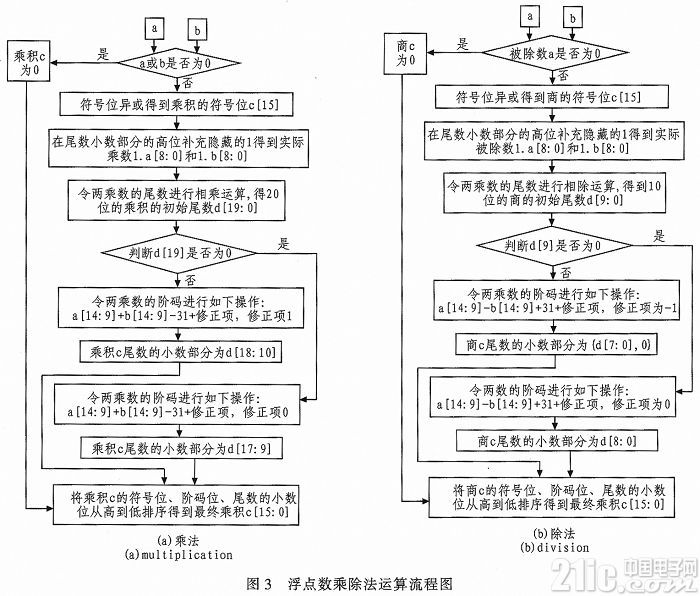

浮点数的乘法运算按照以下步骤进行,其算法流程图如图3所示。

1)判0操作:乘法运算,检查两乘数是否有0,若有,结果为0。除法运算,检查被除数是否为0,若为0,结果为0。

2)符号位操作:对两数的符号位进行异或操作,确定结果的符号位。

3)阶码操作:乘法运算,乘积的阶码是(Ea+Eb-31+修正项);除法运算,商的阶码是(Ea-Eb+31+修正项)。修正项的值由4)中非规格化数调整为规格化数进行的移位个数决定。

4)尾数操作:乘法运算,两乘数尾数的小数部分的高位补1后相乘,得到乘积的20位初始尾数d;除法运算,被除数和除数尾数的小数部分的高位均补1,对1.Ma和1.Mb进行相除操作,令d=1.Ma÷1.Mb,采用移位相减,先比较1.Ma和1.Mb大小,若1.Ma≥1.Mb,则d为1,且令1.Ma=1.Ma-l.Mb;若1.Ma1.Mb,则d为0,且令1.Ma左移一位再次进行比较得到d,依次重复上述比较过程最终得到商的初始尾数d。

5)归一化操作:乘法运算,d[19]、d[18]不同时为0,若d[19]为0,即乘积的整数为01,则乘积尾数的小数部分为d[17:9],修正项为0;若d[19]为1,即乘积的整数为10或11,则将初始尾数右移一位,同时乘积指数加1,修正项为1,乘积尾数小数部分为d[18:10]。除法运算,d[9]和d[8]不会同时为0,若d[9]不为0,商的商的初始尾数的整数为1,尾数小数部分为d[8:0];若d[19]为0,商的初始尾数的整数为0,则将初始尾数左移一位,同时商的阶码减1,修正项为-1,商的尾数小数部分为d[7:0]并在低位补0。

将上述操作结束后得到的符号位、阶码位、尾数的小数部分按照自定义浮点数格式进行排列,得到最终的结果。

3 自定义浮点数运算的仿真机综合分析

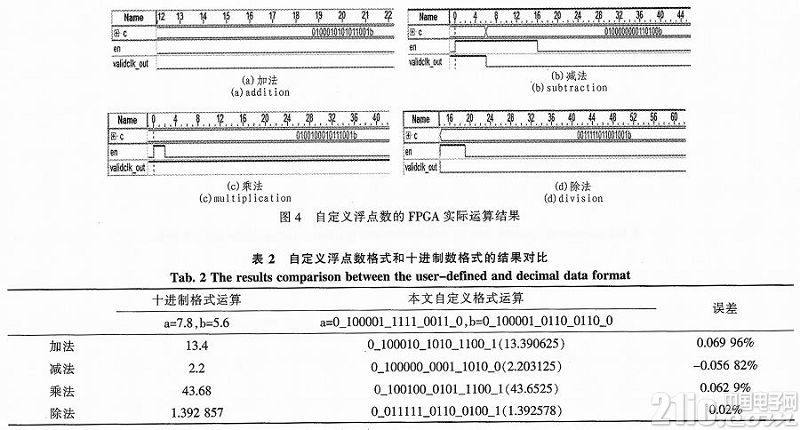

为了验证本文中自定义浮点数运算模块的正确性及其误差大小,且考虑到仿真模型中的变量都为正的浮点数,这里以实数7.8和5.6为例,分别将其变换为本文中自定义的浮点数格式,在自行开发的以EP3C80E484C型号为核心的FPGA上运行,并通过QuartusⅡ软件中自带的debug工具软件查看其运算结果,其中加减乘除运算的部分结果如图4所示。

为了验证FPGA实际运算结果的正确性,将上述浮点数格式的结果转换成十进制格式,并进行系统误差对比,如表2所示。

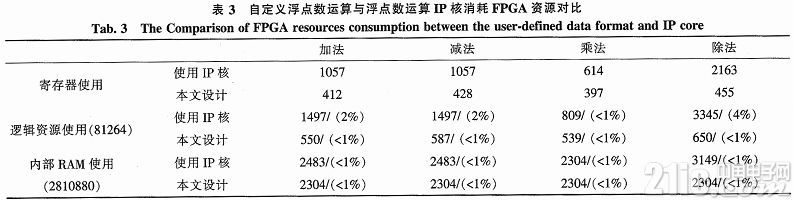

由表2的对比结果可知,在FPGA运行的16位自定义数据格式的加、减、乘、除运算模块的计算误差不超过0.1%,能够满足宏观交通流模型的仿真中对计算精度的要求。此外,在保证模型仿真精度的同时,自定义16位数据格式的加、减、乘、除运算模块与Quartus II软件公开的32位浮点数运算IP核相比,能够显著降低对FPGA资源的消耗,其资源对比如表3所示。

4 模型仿真及综合分析

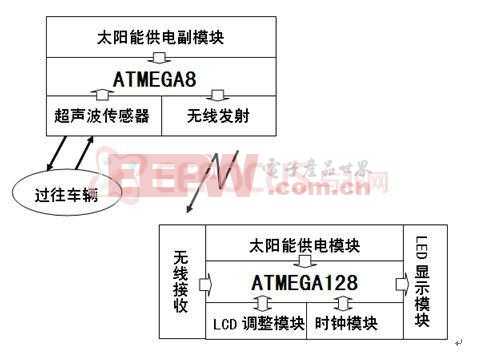

基于自定义浮点数运算模块,前文以Papageorgiou模型为仿真对象,在FPGA上设计了交通流仿真模块。以一段长度为5 km的单向单车道的高速公路为例,将其等分为10段,采用时间设为T=15 s,模型中其他参数设置为:α=0.95,ζ=1,l=1.86,m=4.05,τ=0.005 56 h,ζ=35 km2/h,λ=40 veh/km/lane,Vf=95.1 km/h,kj=110veh/km/ lane。

在初始时刻,假设各路段密度、速度相同,分别为60 veh/km/lane、30 km/h,并假定驶入高速公路的车流量为恒值Q0=1 500 veh/h,每个入口匝道车流量也为恒值r=750 veh/h。

在FPGA上对高速公路宏观模型进行仿真需要注意两个问题:1)边界赋值问题,这里采用边缘赋值条件,令v0(n)=v1(n),k0(n)=Q0/v1(n),k11(n)=k10(n);2)通过多项式拟合方法简化式(4)中指数和底数均为浮点数的幂运算,并由(7)式进行替换。

Ve[ki(n)]=0.008[ki(n)]3-0.064[ki(n)]2+0.371 4[ki(n)]+92.310 3 (7)

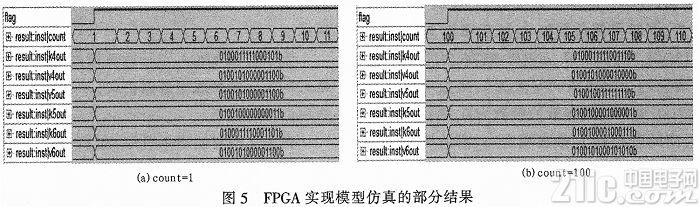

FPGA实现的模型仿真结果如图5所示。

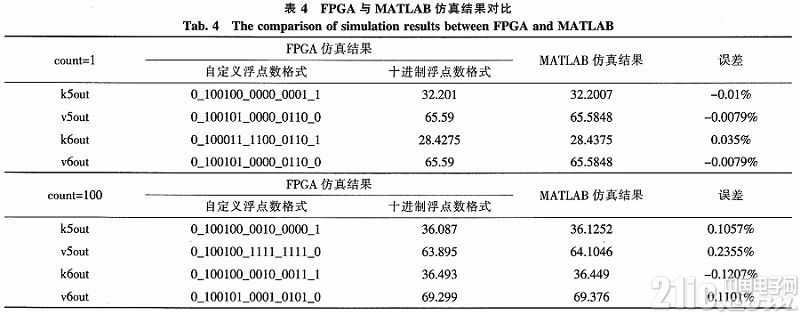

其中flag表示结果输出标志,count是仿真时间间隔的个数,k5out-k6out和v5out-v6out别是第5、6路段的交通流密度和车辆平均速度。为查验FPGA的仿真精度,选取count= 1,100时两组数据,转换成十进制浮点数形式,与MATLABA仿真结果对比,如表4所示。

从表4知,基于FPGA的模型仿真与MATLAB的仿真结果对比,在仿真初期误差几乎为0,随着仿真时间持续增长,误差随之增大,但总体差距不大,能够满足仿真精度的要求。

5 结束语

1)本文设计了基于自定义浮点数的高速公路交通流宏观动态模型仿真,并在自行开发的FPGA电路板上进行了验证,其中自定义浮点数运算实现简单,节省了FPGA逻辑资源,能够在保证计算精度的前提下以较快的速度实现模型的仿真,在后续的交通控制研究中可以进一步在FPGA上实现控制算法的效果验证;

2)本文的不足之处在于没有直接实现底数和指数全为浮点数的幂运算,而是根据所设定的参数进行多项式拟合,导致模型仿真精度在一定程度上受到拟合精度的限制。

评论