一种精确帧同步算法及FPGA实现

在卫星通信系统中,发送端通常利用不同的分组时隙同步传送处在同一传输频带内的各路信号,而接收端为了准确识别和分离出数据流中的各路信号,需要采用帧同步算法进行分组检测和符号同步,其中分组检测用来识别数据分组,符号同步用来寻找到数据分组的确切起点。

本文引用地址:https://www.eepw.com.cn/article/201610/308309.htm本文首先描述了经典帧同步算法原理,然后分析了信道环境对相关性能的影响,给出了在噪声和频偏情况下相关峰值变化规律,最后提出了一种基于分段互相关加分段延迟相关的精确帧同步算法,以及该算法的FPGA实现。

1 经典帧同步算法原理

帧同步算法的基本原理是利用接收信号中帧头序列的相关特性进行能量累积,当检测到相关器产生的能量值大于门限阈值时,就认为检测到数据分组,然后将搜索门限阈值内的最大能量值作为检测到的符号临界点。帧同步算法主要有2类:一类是以帧头自相关为基础的延迟相关算法,该算法具有较大的频率偏移容限,在低信噪比和多径信道下,其自相关曲线在峰值附近变化平缓,无法精确指示帧起始点:一类是以帧头互相关为基础的本地相关算法,该算法具有锐利的尖峰,能准确指示帧起始点,抗噪声和多径能力强,

但是对频率偏移很敏感。

为了改进帧同步算法的性能,一种方法是优化本地相关算法,通过补偿频率偏移来保证锐利的尖峰。文献采用了分段互相关加上能量累积,该算法虽然通过分段降低了频率偏移对峰值幅度的影响,但是它在分段较多时的相关峰就已经不是锐利尖峰,而且采用了能量归一化和固定的门限阈值,既增加了复杂度,又存在一定虚(漏)警风险。文献将接收信号分为多路,采用类似并行扫频的方式,使每一路采用不同的载波频率值对接收信号进行频率补偿,其中必有一路的残余频偏足够小,从而使本地相关算法产生接近无频偏时的锐利尖峰,但该算法的缺点是需要实现足够多的频偏补偿和多路互相关器,否则当残余频偏超过锁相环的捕获带时,后者将无法跟踪频偏。另一种方法是综合采用延迟相关和本地相关算法,即利用延迟相关对频偏的不敏感估计并补偿频率偏移,利用本地相关产生的尖峰搜索精确的帧起始点。文献先采用延迟相关进行分组检测和粗频偏估计,再在频偏补偿后采用互相关的方法完成时间精同步,该算法可使互相关运算避免遭受频偏的影响,但是其用于时间粗同步的自相关方法由于相关峰不尖锐,以及固定的检测门限,仍存在一定的虚(漏)警概率。文献在通过互相关确定了训练序列位置后,先用延迟自相关补偿粗频偏,再用传统方法进行时间同步和精频偏估计,但是该算法的频偏估计性能与延迟相关的延迟距离相关,而且算法的时间代价和硬件代价较大。

2 信道环境对相关性能的影响

在卫星通信系统中,信道环境对相关性能影响很大,主要影响因素有多径效应、阴影效应、多普勒效应,以及系统频偏和信道噪声。由于卫星接收机主要在直射路径下工作,阴影效应相当于增强了传输信号中的背景噪声,多普勒效应相当于在系统频偏基础上叠加一个时变频偏,因此下面主要分析频偏和信道噪声对相关性能的影响。

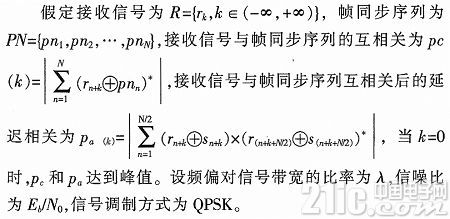

图1给出了N=512、k=0、λ取[-0.1,0.1]时频偏对经典相关峰值的影响,其中横轴每格取值0.001,纵轴等于相关峰与平均幅度之比。可见,延迟自相关峰均比约为18,互相关峰均比约为26,前者基本不受频偏影响,后者在频偏增大时峰均比值剧烈减小。

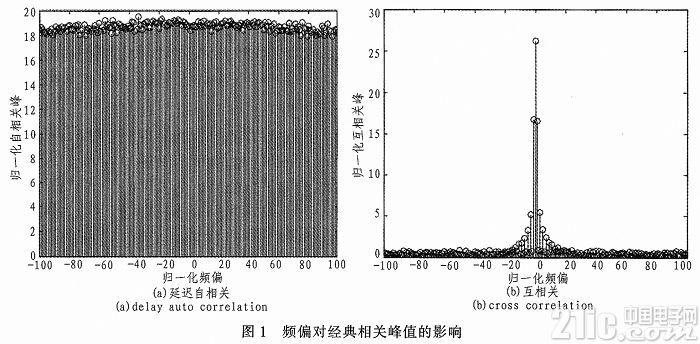

图2给出了N=512、k=0、Eb/N0取[-10,10]dB时噪声对相关峰值的影响,其中横轴每格取值0.1 dB,纵轴不变。可见,峰均比值均随着噪声增强而降低,但是延迟相关峰均比变化率为8倍,互相关峰均比变化率为2.5倍,即延迟相关对噪声更敏感。

3 帧同步算法描述及FPGA实现

3.1 帧同步算法描述

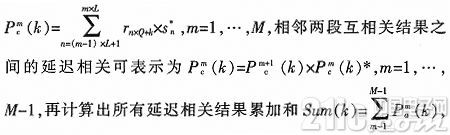

假定过采样倍数为Q,当帧同步序列长度为N时,将本地序列等分为M段,每段长度为L=(N/M)个码片,相关窗总长度等于Q×N,每段相关窗长度为个采样QxL,分别计算出每段接收信号与本地序列的互相关,则第m段互相关结果为

那么相关幅值可表示为Peak(k)=|Sum(k)|,频偏估计值可表示为Foff(k)=arg(Sum(k))/(2πLT),T为码片周期。当本地序列与帧同步序列的最佳采样点完全对齐时,Peak(k)达到最大值,对应的Foff(k)即为频偏估计值。峰值捕获的判决算法可表示为

其中PeakTH为动态门限,它由AGC幅值水平和信噪比估计联合确定。

下面以N=512、M=4、Q=4为例,分析该算法的噪声性能、频偏估计误差和虚警/漏警概率。

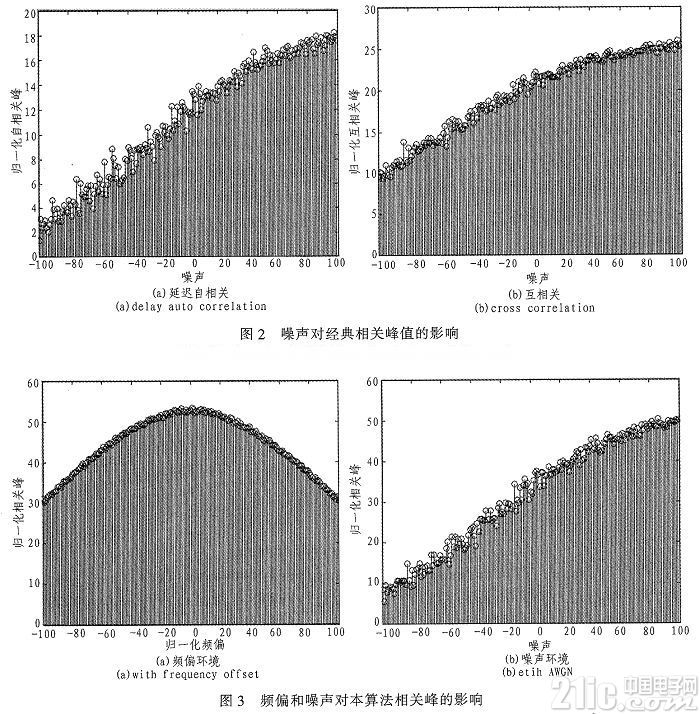

图3给出频偏和噪声对本算法相关峰的影响。在频偏环境下,与延迟自相关相比,在±0.1倍频偏处提高了约2倍。在零频偏处提高了约3倍;与互相关相比,在±0.1倍频偏处提升了至少30倍,在零频偏处提高了约2倍;在噪声环境下,峰均比变化率为5倍,处于延迟自相关和互相关之间。可见本算法显著提升了相关峰均比。

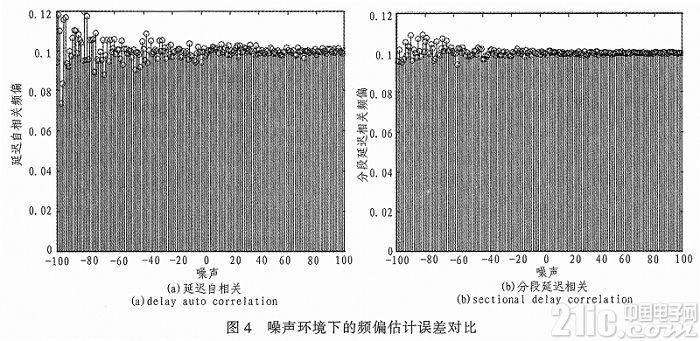

图4给出了延迟相关算法和本算法的频偏估计误差对比,其中横轴表示噪声,取值范围为[-10,+10] dB,纵轴表示频偏估计值,仿真预设频偏为0.1倍载波频率。显然,本算法的频偏估计误差要远小于延迟相关算法。由于互相关算法对频偏敏感,此处不讨论其频偏估计性能。

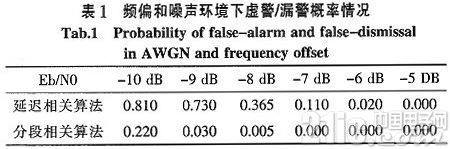

表1给出频偏和噪声环境下延迟相关算法和本算法的虚警/漏警概率情况,其中频率偏移为0.1倍载波频率。

综合上述讨论,本文综合采用了本地PN解扰、分段互相关和分段延迟相关来产生帧检测所需的锐利尖峰,并且该尖峰在低噪声和大频偏环境下依然有效。与文献相比,本算法同时具有更高的峰均比和抗频偏性能,而与文献相比,本算法一次性完成帧头捕获和粗频偏估计,不需要进行多次估计和迭代,大大简化了算法复杂度。

3.2 帧同步算法FPGA实现

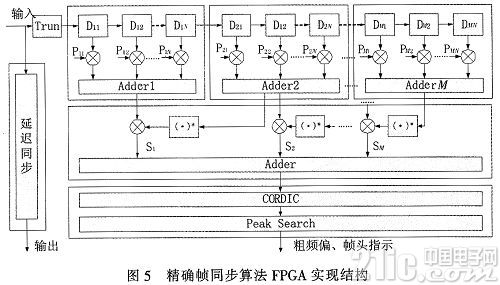

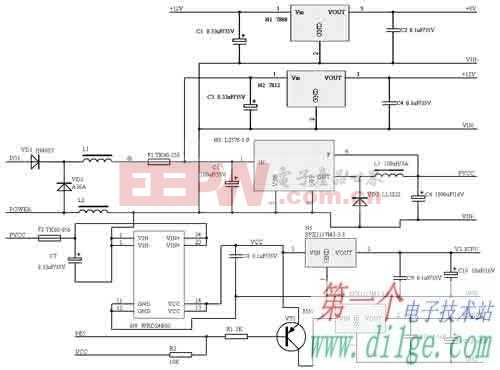

图5给出精确帧同步算法FPGA实现结构。输入数据被分为两路:一路在位宽截短后进行分段互相关,再在相邻的分段互相关结果之间进行延迟相关,然后将延迟相关结果累加后进行CORDIC旋转运算,计算出与延迟相关结果对应的幅值和相位,最后由峰值搜索模块输出帧头指示和粗频偏估计值;另一路用来对输入数据进行延迟同步,使输出数据与粗频偏估计值、帧头指示精确对齐,以便解调帧内有效数据。

如图5所示,本算法主要由延迟同步单元、互相关单元、延迟相关单元、CORDIC旋转计算单元和峰值搜索单元五部分组成。需要注意的是,如果输入数据采用3~5倍过采样,码片同步精度会更高,定时环路也入锁更快,延迟同步单元产生的延迟必须与其他4个单元产生的总延迟严格保持一致,以避免同步到存在相位偏移的码片,而互相关单元长度N和延迟相关单元长度M则是可调参数,使用者可根据帧头结构进行调整。此外,为了降低逻辑资源使用,数据截短的位宽可选择3~6位,其中保留2位符号位,不建议直接采用符号位进行互相关计算。

4 结论

本文提出了一种基于分段互相关加分段延迟相关的帧同步方法,该方法将分段后的接收序列与本地序列互相关,再在相邻互相关结果之间进行延迟相关,累加所有延迟相关结果后求模得到峰值幅度和粗频偏估计值。由于分段后的互相关长度较短,段首和段尾之间由频偏引起的相差很小,保证了每段互相关的幅值基本不受频偏影响,而相邻互相关之间的延迟相关求和既保留了载波频偏信息,又有效积累了能量。测试表明本算法在低信噪比和大载波频偏下依然能产生高质量的锐利尖峰,而且通过采用动态检测门限和AGC,有效降低了虚(漏)警概率,并通过去除多次迭代估计和能量归一化,降低了算法复杂度。该算法适用于卫星信道下连续或突发信号接收处理。

评论