μC/OS-II在ATmega128单片机上的移植与开发

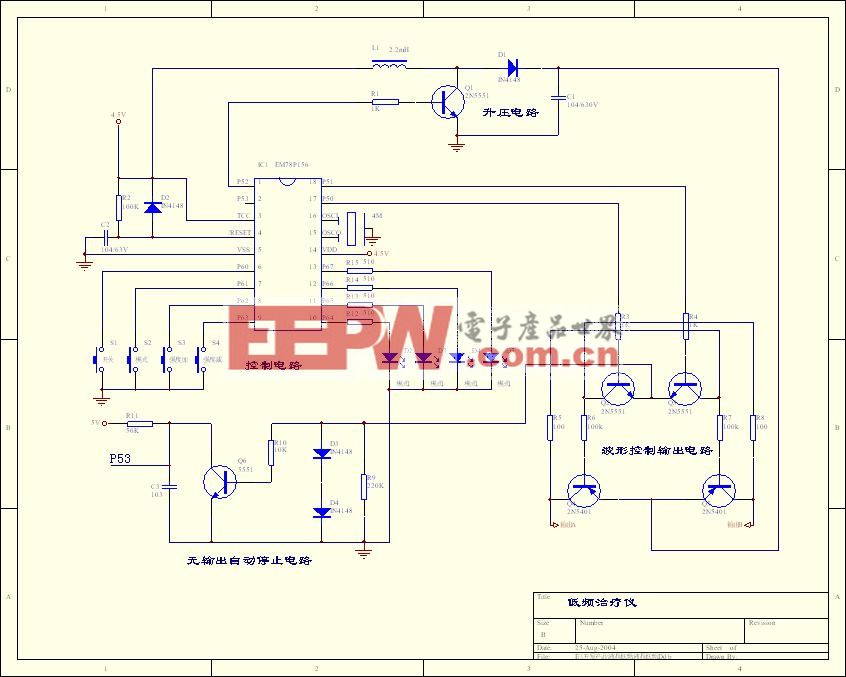

本文首先介绍了实时内核μCOS-II和微处理器ATmega128的特点,论述了在此基础上进行移植,编写API函数,建立自己的RTOS,和用这些API函数建立嵌入式应用系统的方法和步骤。最后总结了运用这一嵌入式应用系统开发便携式医疗设备的优点。

本文引用地址:https://www.eepw.com.cn/article/201610/305930.htm引 言

本文介绍μC/OS-Ⅱ移植到ATMEL公司的8位微控制器ATmega128上的过程。所谓移植,就是使一个实时内核可以在某个微处理器上运行,并在此基础上进行驱动程序开发,使之成为一个实用的嵌入式系统。嵌入式系统包括了硬件和软件两部分,由于系统硬件资源的限制和实际应用的要求,应用系统对软件的基本要求是体积小,执行速度快,具有较好的裁减性和可移植性。

嵌入式系统的软件一般由嵌入式操作系统和应用软件组成,通过在操作系统之上开发应用软件,可以屏蔽掉很多底层硬件细节,使得应用程序调试方便,移植简单,易维护,同时开发周期也短。多数实时操作系统为用户提供一些标准的API函数,程序开发人员可以利用这些API函数进行应用程序开发。但是现在商用型的实时操作系统价格非常昂贵,而免费型的实时操作系统μCOS-II作为一个源代码公开的实时内核已经有了10余年使用实践,许多行业都有成功应用该内核的实例。但由于μCOS-II只是一个实时内核,它没有像商用型实时操作系统那样提供API函数接口,有很多工作需要用户去完成,还需要根据实际应用需要进行功能扩展,包括底层的硬件驱动、文件系统、用户图形接口等程序的编写。

μC/OS-II嵌入式实时操作系统简介

μC/OS-II是著名的、源码公开的实时内核,可用于各类8位、16 位、32位单片机或DSP。μC/OS-II是一个完整、可移植、可固化、可裁减的占先式实时多任务内核。它用ANSIC语言编写,包含小部分与硬件有关的汇编代码,使之便于移植,可以在不同架构的微处理器上使用。到目前为止,该内核已有10多年的应用史,在医疗、网络、通信等许多领域得到了广泛应用。μC/OS-II内核可以分为几个独立的部分,分别是任务管理、时间管理、任务间通信、内存管理几个独立的部分,他的许多功能都是可配置的,这样可以根据应用的需要对操作系统进行裁减。μC/OS-II是占先式实时内核,他总是运行在就绪条件下优先级最高的任务,μC/OS-II总共可以管理64个任务,赋予每个任务的优先级必须是不同的,每个任务都有自己独立的堆栈,可以压低用户程序对内存的需求。全部μC/OS-II的函数调用与服务执行时间具有可确定性,它的系统服务的执行时间不依赖于应用程序任务的多少。μC/OS-II中的任务可以是一个无限的循环,也可以在执行完一次后被删除掉,任务在休眠、就绪、运行、等待和挂起等几个状态之间进行转换。μC/OS-II要求用户提供定时中断来实现延时和超时控制等功能,这个定时中断称为时钟节拍,他的实际频率由用户的应用程序决定,一般为10~100Hz 。节拍频率越高,系统的负荷越重。μC/OS-II中有三种用于数据共享和任务通信的方法:信号量、邮箱和消息队列。一个任务或者中断服务子程序可以通过事件控制块向另外的任务发信号;一个任务可以等待另一个任务或中断服务子程序给它发送信号;或者是多个任务等待同一个信号的发生,在这种情况下,优先级最高的任务将得到这一信号并进入就绪状态准备执行。

ATmega128微处理器的硬件特点

ATmega128的MCU包括一个算术逻辑单元(ALU) ,一个状态寄存器(SREG) ,一个通用工作寄存器组和一个堆栈指针。状态寄存器(SREG) 的最高位I是全局中断允许位。如果全局中断允许位为零,则所有中断都被禁止。当系统响应一个中断后,I位将由硬件自动清“0”;当执行中断返回(RETI) 指令时,I位由硬件自动置“1”,从而允许系统再次响应下一个中断请求。通用工作寄存器组是由32个8位的通用工作寄存器组成。其中R26~R31这6 个寄存器还可以两两合并为3 个16位的间接地址寄存器,这些寄存器可以用来对数据存储空间和程序存储空间进行间接寻址的寄存器。堆栈指针(SP) 是一个指示堆栈顶部地址的16 位寄存器。ATmega128单片机的硬件堆栈的生长方向是向下的(从高地址向低地址生长) ,所以软件堆栈在定义的时候,也要采取相同的生长方向。ATmega128单片机的数据存储器是线形的,从低地址到高地址依次是CPU寄存器区(32个通用寄存器) ,I/O寄存器区,数据存储区。

ATmega128的中断响应机制

ATmega128有34个不同的中断源,每个中断源和系统复位在程序存储空间都有一个独立的中断向量(中断入口地址) 。每个中断源都有各自独立的中断允许控制位,当某个中断源的中断允许控制位为“1”且全局中断允许位I也为“1”时,系统才响应该中断。当系统响应一个中断请求后,会自动将全局中断允许位I清零,此时,后续中断响应被屏蔽。当系统执行中断返回指令RETI时,会将全局中断允许位I置“1”,以允许响应下一个中断。若用户想实现中断嵌套,必须在中断服务子程序中将全局中断允许位I置“1”。在中断向量表中,处于低地址的中断具有高的优先级。优先级高只是表明在多个中断同时发生的时候,系统先响应优先级高的中断,并不含有高优先级的中断能打断低优先级的中断处理工作的意思。由于μC/OS-Ⅱ的任务切换实际上是模拟一次中断,因此需要知道CPU的中断响应机制。中断发生时,ATmega128按以下步骤顺序执行:

(1) 全局中断允许位I清零。

(2) 将指向下一条指令的PC值压入堆栈,同时堆栈指针SP减2。

(3) 选择最高优先级的中断向量装入PC,程序从此地址继续执行中断处理。

(4) 当执行中断处理时,中断源的中断允许控制位清零。中断结束后,执行RETI指令,此时:

①全局中断允许位I置“1”。

② PC从堆栈推出,程序从被中断的地方继续执行。特别要注意的是:ATmega128A单片机在响应中断及从中断返回时,并不会对状态寄存器SREG 和通用寄存器自动进行保存和恢复操作,因此,对状态寄存器SREG 和通用寄存器的中断保护工作必须由用户来完成。

ATmega128的定时器中断

ATmega128有三个定时器:T0,T1,T2,可以为μCOS-II提供精确的时钟源。ATmega128的三个定时器都有计数溢出中断功能,而且T1和T2还有匹配比较中断,即定时器计数到设定的值时,产生中断并自动清零。若系统采用这种中断方式,其好处是在中断服务程序ISR中不需要重新装载定时器的值。

评论