基于ARM7的高精度频率计的设计

0 引言

本文引用地址:https://www.eepw.com.cn/article/201609/303797.htm频率是人们工作和生活当中常用到的物理量之一。其中时间、速度等物理量都可以用频率来表示。近年来随着现代工业的发展,高精度的频率计得到广泛的重视与应用,比如各大高校和科研院所的实验室需要用到的频率计基准。但是目前能够满足高精度测量要求的频率计结构复杂而且价格昂贵,因此设计一款精度高、成本低的频率计就十分必要了。

直接计数法是过去经常用到的测量频率的方法。直接计数法包括两种测量原理,一种测量原理是在闸门时间T不变的情况下,对被测频率进行计数,通过所计的脉冲数N与T的比值求出相应的频率值;另一种原理是在给定的一个被测信号周期内对标准频率进行计数,通过所计的数值N0与标准频率值求出被测频率。但它们都存在±1个字的计数误差。测量精度低。其次是多周期同步测量法,此方法又叫作倒数计数器法。它是目前频率测量中应用最为广泛的测频方法。多周期同步测量法的测量原理是在若干个给定的被测信号的周期中对标准频率和被测频率同时计数,根据所测得数值求出被测频率。它让不同的被测频率与实际闸门同步,这样就去除了被测频率的±1个字的计数误差,但标准频率依然还存在±1个字的计数误差。此外还有游标法和模拟内插法,这两种方法分别通过游标振荡器和内插器来减小±1个字的计数误差,能够达到很高的精度,但是仪器结构复杂而且成本很高。

本文利用相位检测技术,通过捕捉标准信号和被测频率的相位重合点,使这两个频率和实际闸门完全同步,从而消除了标准频率和被测频率中的±1个字的计数误差,使测量中的精确度能够达到10-10量级。但传统频率计的核心硬件设计大都使用16位单片机外接级联的计数器,这样不仅使电路复杂,引入不必要的误差,无法保证测量精度,而且处理测量数据速度过慢,在当今科研工作中已经无法达到科研人员的科研要求。本文在此基础上通过选用32位处理器ARM7作为主控芯片,比传统的16位单片机提高了控制系统和测量数据处理的速度。

1 相频检测法原理及误差分析

在相位检测法频率测量中有一个重要的概念就是最大公因子频率。它的倒数为最小公倍数周期Tp。最大公因子频率的定义为:如果对于任意两个频率信号和f1和f2,当f1=M f0,f2=Nf0;其中M和N这两个正整数没有公共的约数,那么f0就是f1和f2之间的最大公因子频率fp。两个信号的量化相移分辨率设为![]() ,其公式如下:

,其公式如下:

在一个Tp周期中有M个f1的周期或者N个f2的周期T2。假设M>N且以f2的上升沿作为参考,那么量化后的f1和f2在一个Tp周期中有且只有N种相位差情况,并且每种情况在一个Tp周期中各不相同。若按大小表示则为

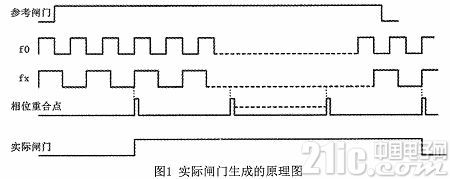

。当两个信号相位差十分小时,称之为相位重合点。相位检测测频的原理就是捕捉若干个相位重合点,在这些相位重合点之间有完整的整数倍标准信号和被测信号的周期,以此来设定实际的闸门时间。这样就可以消除标准频率和被测频率中都存在±1个字的计数误差。图1为实际闸门生成的原理图。

从图1可以看出,当参考闸门打开之后,首个相位重合点到来时,实际闸门开始计数,当参考闸门闭合后首个相位重合点到来时,实际闸门闭合停止计数。当实际闸门开启时,计数器开始分别对标准频率和被测频率计数,假设标准信号脉冲个数为N0,被测信号脉冲个数为Nx,那么被测信号频率值为:

因为δQ要远远小于Tx和T0,所以此方法能够获得相当高的测量精确度。在多周期同步测量中的相对误差与式(6)相同。其中的δN0=±1而δNx=0,所以此倒数计数器法在省略标准频率的影响下测量相对误差为:

由式(11)可知,被测信号的相对误差由标准信号的周期的±1倍所引起。因此将被测频率与标准频率同时同步后测量的值要更精准。

2 硬件电路设计

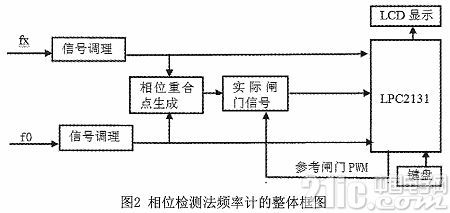

图2为相检频率计的整体框图。由于被测信号要求最大测量频率为10MHz,测量精度达到10-10量级,因此标准信号频率精度要至少达到10-11量级。基于此本文选用安捷伦公司生产的恒温晶振10811A作为标准频率的输出设备,其最大输出频率为10MHz,准确度优于10-11。同时其具有体积小、便于产品设计的优点,因此满足设计要求。

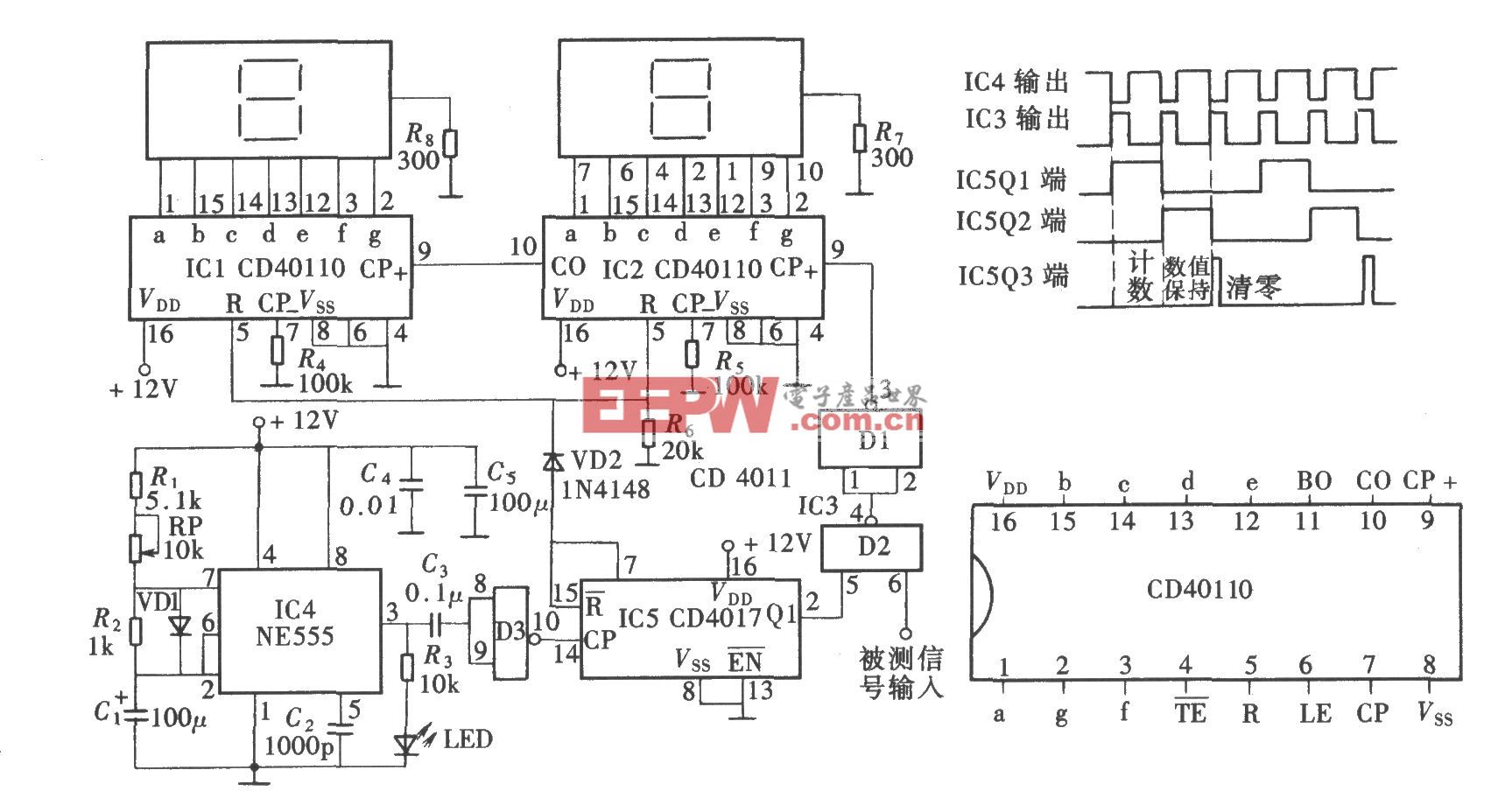

其中频率经过信号调理电路的目的是对输入的信号进行必要的整形与放大。它的输入阻抗以及输入电压的灵敏度要高,以及能够调理各种波形的周期性信号,其中良好的抗干扰能力也是必不可少的。因此本设计选择应用比较器ADCMP604实现信号调理功能,将信号整形为方波信号。ADCMP604的延迟时间大约为1.6ns,与被测信号10MHz相比可以忽略不计。与此同时,电路在抑制共模干扰方面决定采用LVDS差分信号输出来实现。电路图如图3所示。其中Vp端接被测信号,Vn端接地,当fx大于0时,Q端输出为高电平,当fx小于0时,Q端输出为低电平。

评论