基于SoC+FPGA平台快速动态加载驱动开发及实现

摘要:以TI公司的OMAP-L138型号双核处理器单片系统(SoC)与ALTERA公司 EP3C80F484型号FPGA为核心的嵌入式硬件平台,介绍了SoC与FPGA通过高速SPI接口实现固件动态加载的方法,以及基于Linux的SoC对FPGA快速动态加载驱动程序开发的原理及步骤。实际测试基于高速SPI接口的FPGA固件动态加载功能快速稳定,对同类型嵌入式平台的FPGA固件动态加载驱动开发具有借鉴意义。

本文引用地址:https://www.eepw.com.cn/article/201605/291764.htm引言

OMAP-L138双核处理器是TI公司推出的新一代低功耗单片系统(SoC),广泛应用于通信、工业、医疗诊断和音视频嵌入式设备,其内部集成的ARM核与DSP核协同工作,既能满足基于嵌入式操作系统的通用应用程序开发,又能满足专属复杂算法的高效实时运行,再加上大容量FPGA芯片做数字信号的前端处理,可作为较高速率的综合通信数据业务处理通用数字平台。实现对FPGA芯片的固件动态加载,既可以去掉FPGA芯片外挂用于存储其固件的FLASH芯片以降低成本,又可以满足动态改变FPGA运行程序以实现多种应用场合快速灵活的切换要求。

1 OMAP-L138及Cyclone III系列FPGA的特点

采用OMAP-L138与EP3C80F484为核心的嵌入式平台,能为宽带通信设备提供完美的平台解决方案。OMAP-L138的特点[1]如下:

(1)内部集成RISC MPU,即主频为375/456MHz的ARM926EJ-S,以及定/浮点兼容的VLIW DSP,即主频为375/456MHz 的C674x,可满足系统的非实时、多任务及实时、高强度数据处理的应用需求;

(2)强大丰富的外设资源。主要包括:1个EMAC控制器;1个USB2.0接口和1个USB1.1接口;2个I2C接口;1个McASP;2个McBSP;2个SPI接口;4个64位通用定时器;1个实时时钟(RTC);1个可配置的16位HPI;144个可配置的GPIO管脚;3个UART接口;2个eHRPWM和3个eCAP;1个EMIFA口,可接16位SDRAM/NOR Flash/NAND Flash;1个EMIFB口,可接16位的DDR2(最高频率150MHz)或16位 MDDR (最高频率133MHz);2个MMC/SD/SDIO;1个 LCD控制器;1个SATA控制器;1个UPP接口;1个VPIF接口;众多外设可以通过PSC(电源及睡眠控制)和管脚复用控制,根据系统需求灵活配置;

(3)高效的缓存机制。其中ARM核内部有16KB的L1程序Cache和16KB的数据Cache,以及8KB中断向量表存储RAM;DSP核采用二级缓存结构,包括32KB 的L1程序Cache、32KB 的数据Cache和高达256KB可灵活配置的L2 Cache,L2可以被ARM核访问;此外在两核之间还有128KB的片内SHARE RAM,可用于ARM核和DSP核高速交换数据,而不影响各自的运行;

(4)低功耗设计。采用1.2V内核电压,1.8V或3.3V 可配置I/O接口电压。

FPGA芯片EP3C80F484为ALTERA公司推出的Cyclone III系列FPGA的一员,其特点[2]如下:

1)Cyclone III满足高性能、低功耗、低成本的应用需求;

2)提供容量为5000至200000个逻辑单元、0.5MB至8MB片内RAM的系列芯片选择,其低功耗设计更易于满足设计预算,其中EP3C80F484内部集成81264个逻辑单元,2810880 比特内部RAM,484个管脚;

3)提供高、中、低I/O管脚封装以满足不同应用场合;

4)多达4个PLL(锁相环)为片内时钟、片外时钟及I/O接口,提供稳定的时钟管理及同步;

5)支持32位Nios II嵌入式处理器,可在单片上集成Nios II软核、片上外设及内存、片外内存接口[3],提供低成本可定制的嵌入式处理解决方案;

6)提供多种高速内存接口,例如DDR、DDR2、SDR、 SDRAM以及 QDRII SRAM。

2 OMAP-L138对EP3C80F484实现快速动态加载的方法

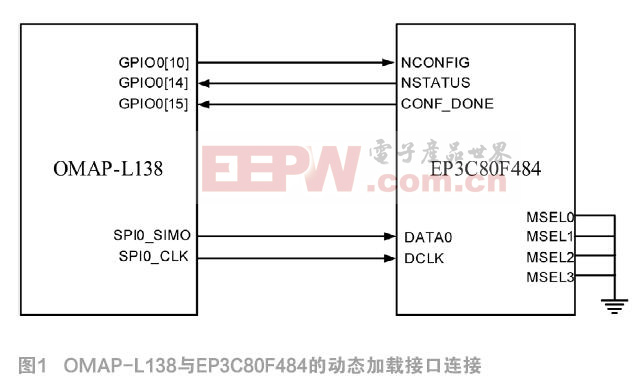

Cyclone III系列FPGA的程序加载运行主要通过以下几种方式:主动串行(AS)、主动并行(PS)、被动并行 (FPP)、被动串行(PS)以及通过JTAG接口采用USB下载线进行加载。当OMAP-L138对EP3C80F484进行动态加载时,采用的是被动串行(PS)模式,因此对应的EP3C80F484的4位MSEL配置管脚接地。为提高加载的速度及准确性,采用OMAP-L138的SPI0接口的SPI0_CLK及SPI0_SIMO管脚与EP3C80F484配置口的DCLK及DATA0管脚连接,EP3C80F484配置口的其它控制管脚与OMAP-L138的GPIO管脚连接,遵从Cyclone III系列FPGA的PS模式加载时序要求实现对FPGA的快速动态加载。OMAP-L138与EP3C80F484的连接如图1所示。

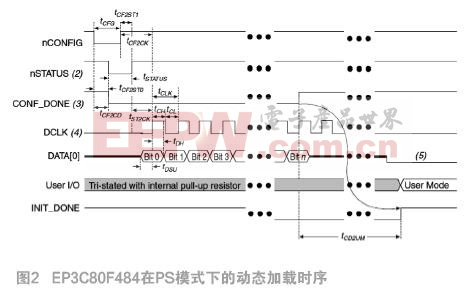

EP3C80F484在被动串行(PS)模式下的动态加载时序要求如图2所示。

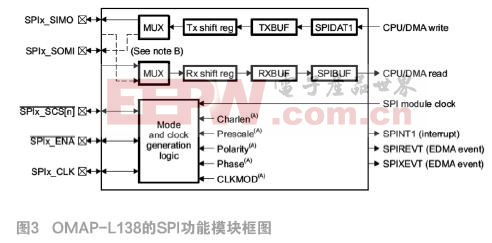

采用OMAP-L138的SPI0接口与EP3C80F484连接,可以使用其高达50Mbit/s的高速数据传输能力,实现EP3C80F484的快速动态加载。OMAP-L138的SPI功能模块框图如图3所示。

SPI控制器包含收发移位寄存器、缓存以及控制逻辑,数据在传输开始时写入发送移位寄存器,在数据传输结束时读取接收缓存。SPI控制器可工作在主模式和从模式,工作在主模式时由SPI控制器发起传输并驱动SPIx_CLK管脚产生时钟。支持多种数据格式配置,四种相位及极性配置选项[4]。

3 EP3C80F484动态加载基于Linux内核的驱动开发

动态加载驱动本质上属于字符设备驱动,动态加载的驱动开发主要包含两个部分: (1)根据EP3C80F484的动态加载时序要求配置OMAP-L138的SPI0及其它控制逻辑GPIO,实现固件程序的比特流正确灌入EP3C80F484的配置口;(2)实现EP3C80F484的.rbf格式固件加载文件的读取及解析,并传递给底层SPI控制驱动程序实现比特流的传输,完成字符设备各个操作函数的具体实现,并编译成可动态加载的模块驱动文件。

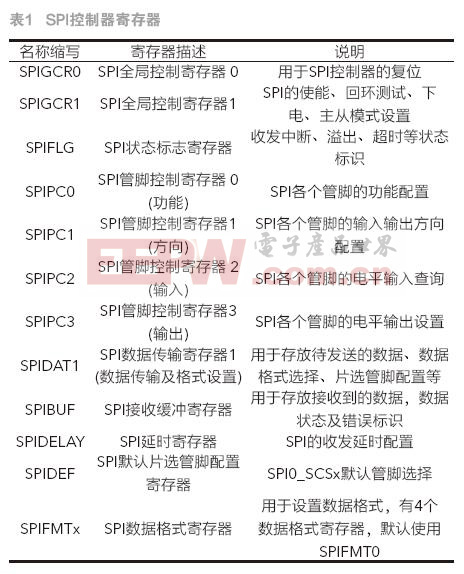

与驱动开发密切相关的主要SPI控制器寄存器说明如表1所示。

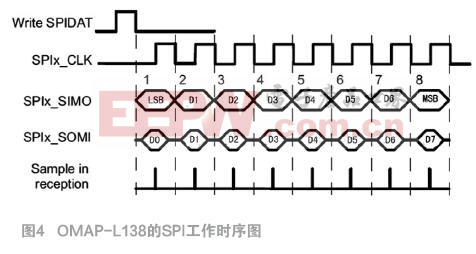

根据EP3C80F484在被动串行(PS)模式下的动态加载时序要求,SPI控制器工作在POLARITY = 0 ,PHASE = 1,SHIFTDIR=1模式,POLARITY、PHASE及SHIFTDIR设置位于SPIFMT0寄存器,工作时序如图4所示。

动态加载字符设备的操作函数中的成员函数实现成为了驱动程序开发的关键,file_operations[5]定义如下:

static const struct file_operations load_fpga_fops =

{ .owner = THIS_MODULE,

.read = load_fpga_read,

.write = load_fpga_write,

.ioctl = load_fpga_ioctl,

.open = load_fpga_open,

.release = load_fpga_release,

};

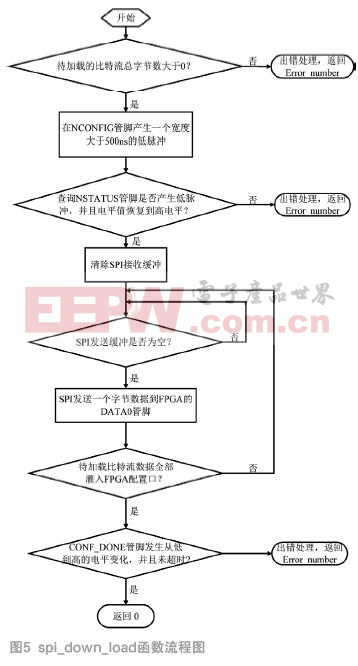

驱动模块的初始化函数load_fpga_init除完成字符设备的设备号及内存申请和设备注册外,还要完成SPI0控制器的所有初始化配置及GPIO管脚配置;load_fpga_write成员函数实现存放于文件系统的.rbf固件加载文件从用户空间到内核空间的数据拷贝,并将基于SPI的动态加载驱动实现封装成功能函数spi_down_load供load_fpga_write函数调用;load_fpga_ioctl成员函数提供SPI通信速率等相关配置。spi_down_load函数流程图如图5所示。

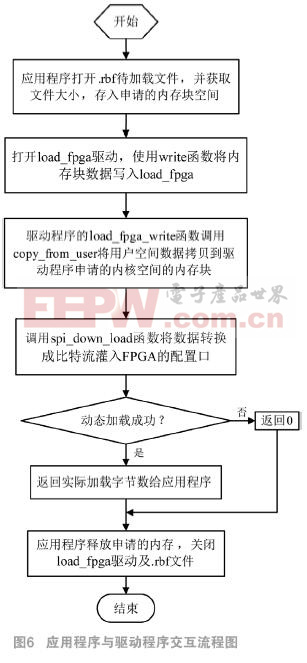

EP3C80F484配置口DCLK最大支持133MHz的比特流,将OMAP-L138的SPI0_CLK配置成50MHz的时钟频率,加上操作系统、文件处理及控制逻辑等开销,对于2MB左右的.rbf固件程序实测动态加载完成耗时小于1.2秒。测试应用程序与驱动程序交互流程如图6所示。

4 结语

本文详细介绍了在Linux环境下,采用型号为OMAP-L138的SOC的SPI接口及逻辑GPIO实现对EP3C80F484的快速动态加载的驱动程序开发的具体方法。该方法可靠、快速且稳定,比纯粹使用GPIO模拟加载时序快一个数量级以上,并在苛刻的使用条件下仍然表现出良好的稳定性。可用于手持终端、车载、船载系统等通信和工业领域,对动态加载嵌入式系统开发具有重要意义。

参考文献:

[1]OMAP-L138 C6-Integra DSP+ARM Processor (Rev. D) . Texas Instruments, 2011.

[2]Cyclone III Device Handbook. Altera Corporation, 2012.

[3]Nios II Processor Reference Handbook. Altera Corporation, 2011.

[4]TMS320C674x/OMAP-L1x Processor Serial Peripheral Interface (SPI) User's Guide. Texas Instruments.2010.

[5]宋宝华. Linux设备驱动开发详解[M]..北京:人民邮电出版社:2008.

本文来源于中国科技期刊《电子产品世界》2016年第5期第40页,欢迎您写论文时引用,并注明出处。

评论