基于FPGA的可调信号发生器

摘要:基于FPGA的应用技术,采用Altera公司DE2-70开发板的CycloneⅡ系列EP2C70作为核心器件,设计了一种基于FPGA的新型可调信号发生器。通过QuartusⅡ软件及Vetilog HDL编程语言设计LPM_ROM模块定制数据ROM,并通过地址指针读取ROM中不同区域的数据,根据读取数据间隔的不同,实现调整频率功能,该系统可产生正弦波、方波、三角波和锯齿波4种波形信号,并使用嵌入式逻辑分析仪对产生的不同波形信号进行实时测试,实验证明,该可调信号发生器系统软件模拟数据和理论定制波形相吻合。

关键词:信号发生器;EP2C70;Vetjlog HDL;FPGA

传统信号发生器大多由模拟电路构成,存在连线复杂、调试烦琐且可靠性较差等缺点。以Verilog HDL编程语言和FPGA器件为核心的可调信号发生器的设计实现,提高了系统可靠性,实现了系统信号实时快速测量,也为其广泛应用于实际领域创造了条件。

1 系统总体设计

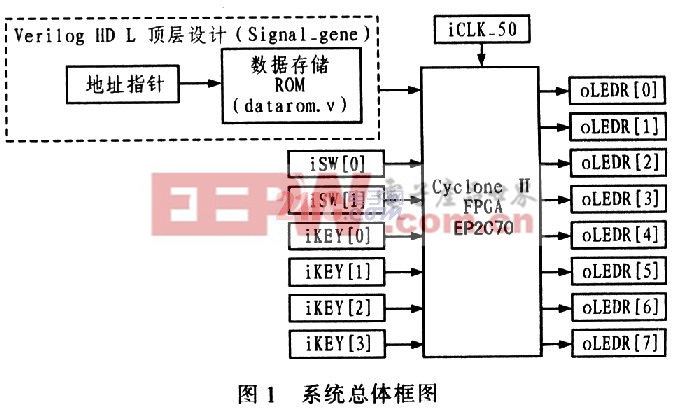

可调信号发生器系统由顶层模块、EP2C70器件、控制开关和输入输出模块等部分组成,如图l所示。在FPGA中实现的顶层文件包含地址指针和数据ROM2部分。其中,数据ROM由QuartusⅡ软件中的LPM_ROM模块构成,能达到最优设计,LPM_ROM由FPGA中的EAB或ESB实现。数据ROM中存储正弦波、方波、三角波和锯齿波4种信号各1个周期的波形数据(在此选择1个周期128个数据样点),地址指针读取ROM中不同区域的数据,可产生不同的波形,并通过使用嵌入式逻辑分析仪SignalTapⅡ进行实时测试。根据读取数据间隔的不同,即可实现调整频率的功能。

2 系统功能模块设计

可调信号发生器系统的功能模块主要由顶层文件(Verilog HDL源程序)和波形数据ROM两部分组成。波形数据ROM设计主要包括设计波形数据ROM初始化数据文件和定制ROM元件(datarom.v)。

2.1 顶层文件设计

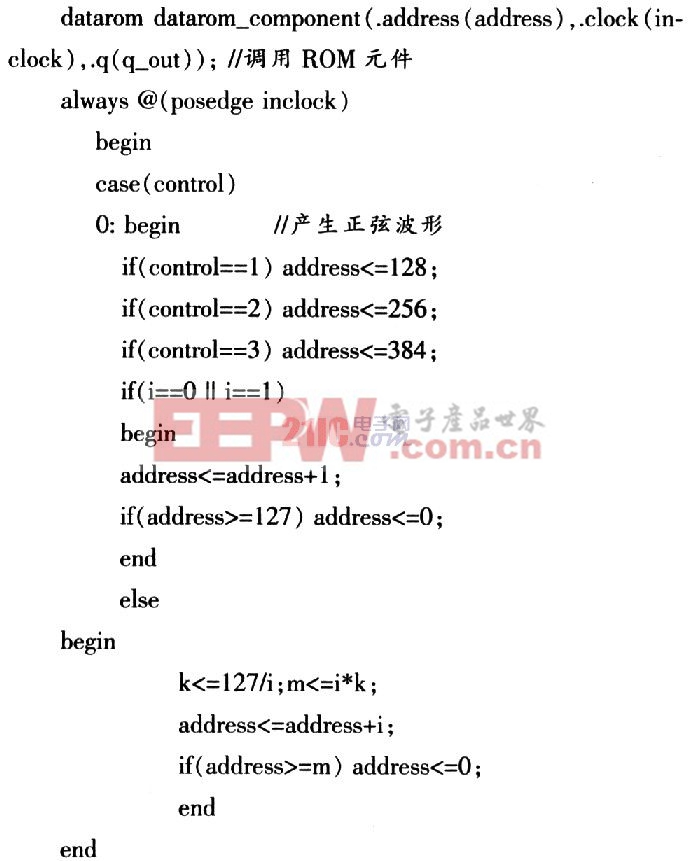

本系统采用Ahera公司的CycloneⅡ系列EP2C70器件作为核心,通过QuartusⅡ软件编写Verilog HDL源程序,实现一个可以产生正弦波、方波、三角波和锯齿波4种波形信号,并且能够实现信号转换及频率可调功能的信号发生器。其中control控制产生波形的种类,00、0l、10、11分别产生正弦波、方波、三角波和锯齿波;i控制读取数据间隔,调整频率。产生正弦波的源程序如下:

评论