基于FPGA的160路数据采集系统设计

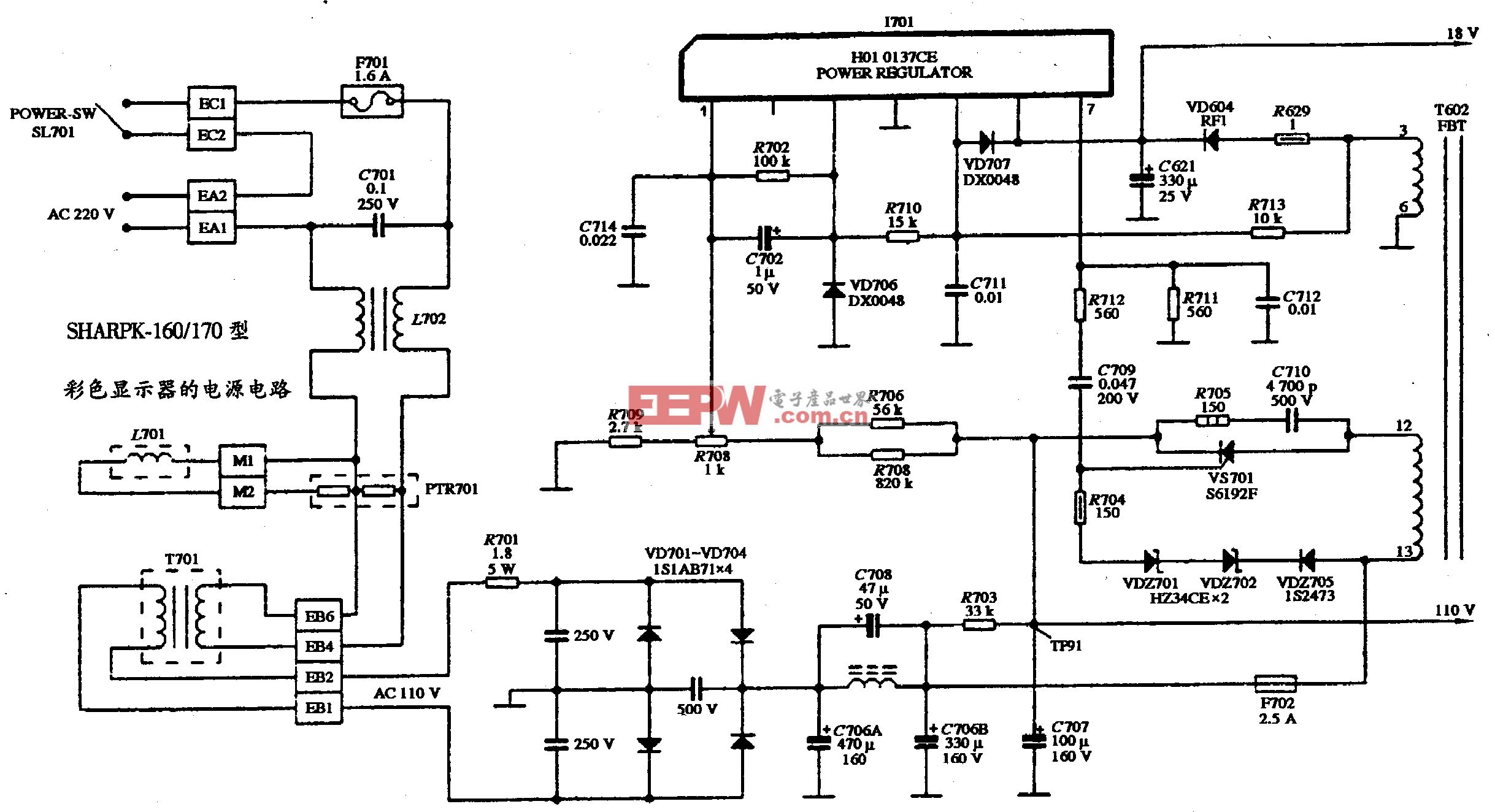

随着科学技术和国民经济的发展,电能需求量日益增加,对电能质量的要求也越来越高。这对电能质量的监测提出了挑战。电能质量的监测往往需要多通道数据采集,但因其覆盖面积大,周期性强,采集数据量大,因此对数据采集系统的采集、传输速度和精度提出了较高的要求。常用的数据采集方案往往采用单片机或数字信号处理器(DSP)作为控制器。以控制模数转换器(ADC)、存储器和其他外围电路的工作。但因单片机自身指令周期及处理速度的影响,很难达到多通道高速数据采集系统的要求,虽然DSP可以实现较高速的数据采集,但在提高其速度的同时,也增加了系统成本。现场可编程门阵列(FPGA)以其时钟频率高,内部延时小,速度快,效率高,组成形式灵活等特点在高速数据采集方面有着单片机和DSP无法比拟的优势。

2 多路信号采集原理

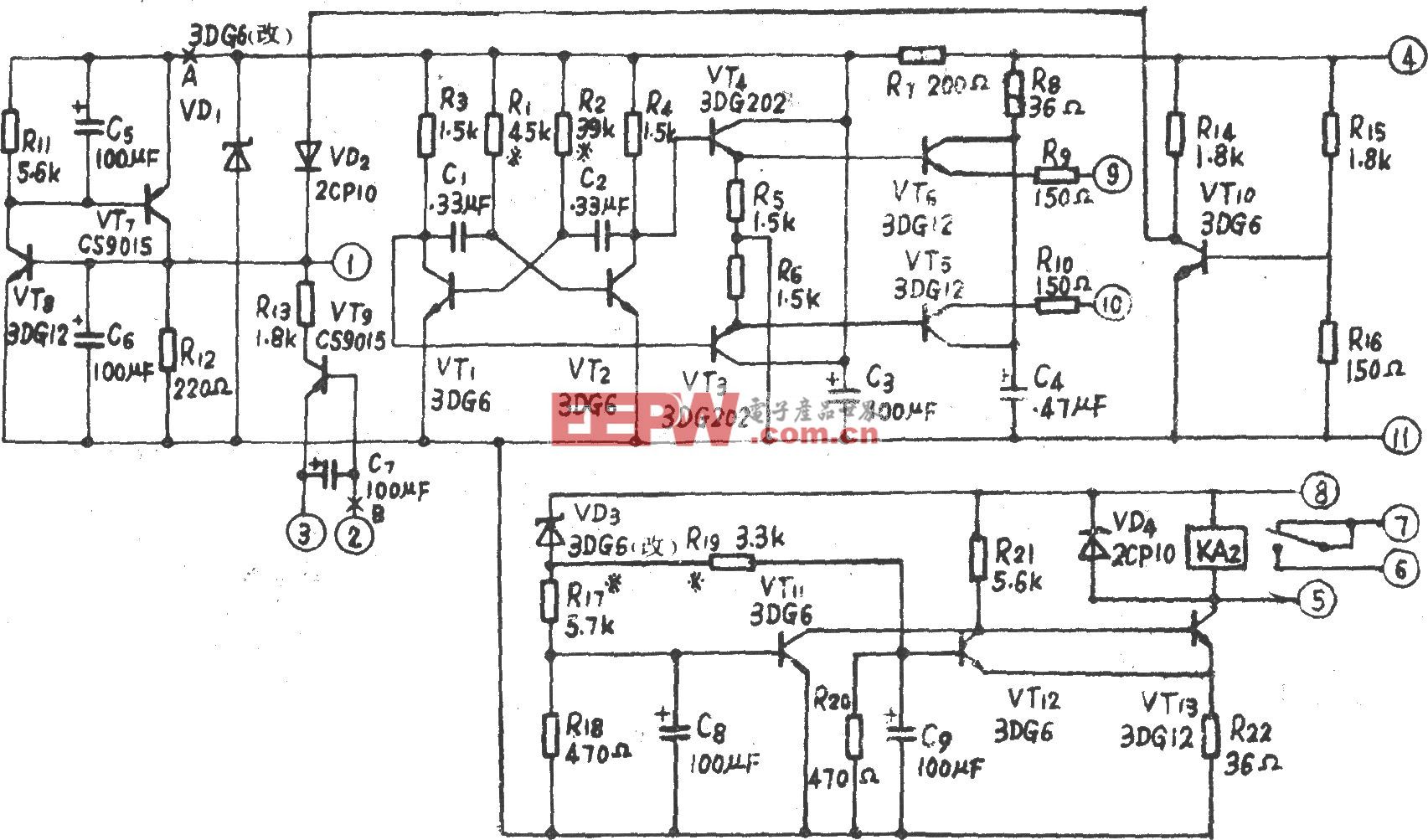

图1示出多路高速数据采集系统的硬件结构。160路信号经过低通滤波器和输出跟随器到多通道模拟开关,并由FPGA控制逻辑选通模拟开关.每次只选通一路,经A/D转换后存入存储器。

3 开关与FPGA控制逻辑的连接

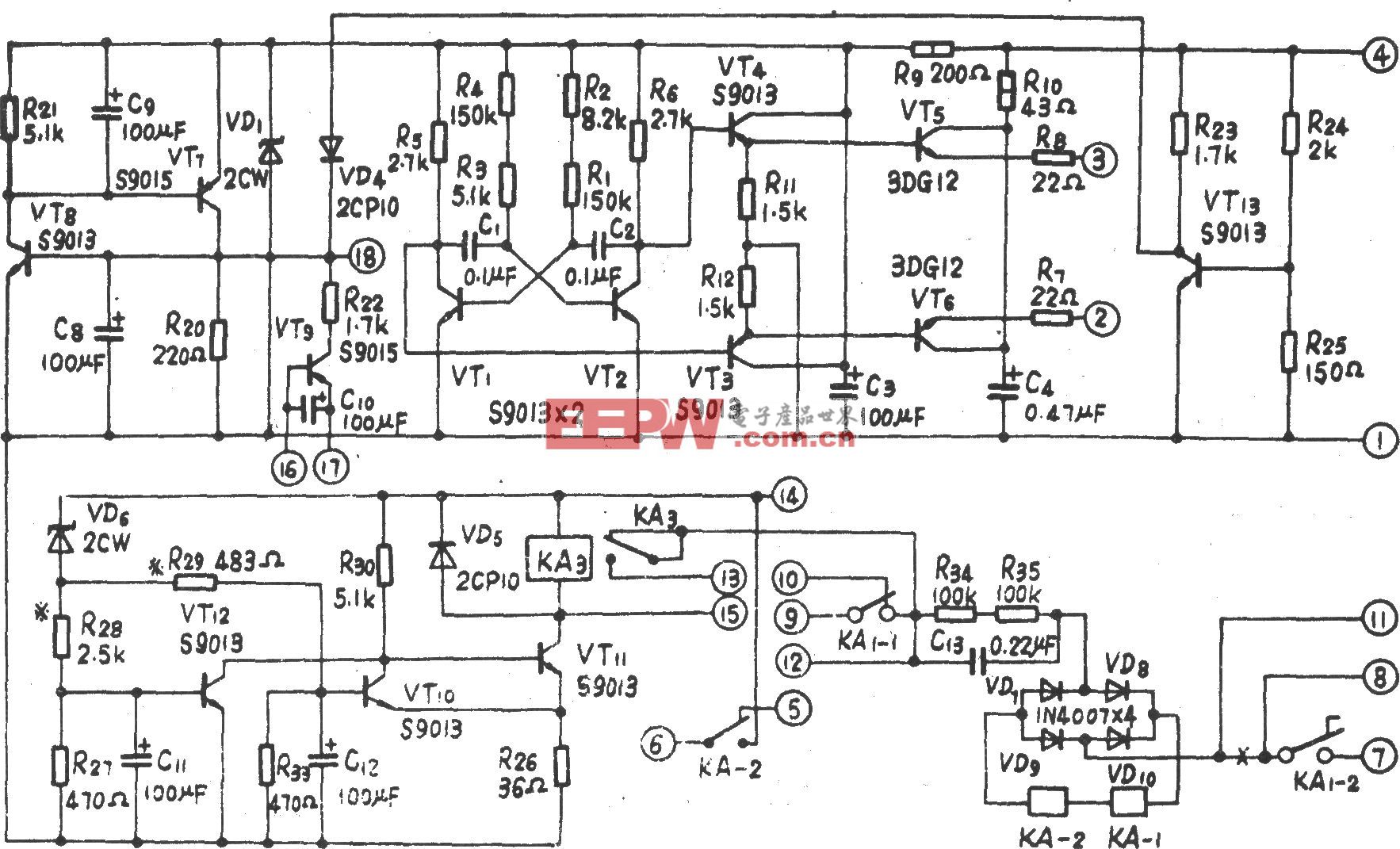

图2a中ADG506是一个能选通16路信号的开关。系统中使用了10片ADG506。通过FPGA控制ADG506的使能端实现开关的选通。ADG506的18引脚是使能端,高电平有效。利用图2b中的ENl~ENl0控制可实现10片ADG506的选通;利用A0~A3编码可实现信号的选通。A0~A3的值是在0000时选通S1信号,依次类推,在1111时选通S16信号。该系统的时钟是40 MHz,采样率为500 kHz,每一路信号采集10个点,共采集160路。A0~A3取决于f_channel的低4位;ENl~ENl0取决于f_channel的其他位数。图3给出程序流程图。

4 时间计算

用于该采集系统中的电子开关,其导通时的触点电阻约为400Ω,关断电阻大于1 kΩ;引脚集成电容为30 pF;运放采用AD824,其输入阻抗大于1013Ω。由此电容的充电过程为:

电容的漏电过程为:

由于共有192组跟随电路,故条件t2≥192t1成立。其中式(2)和式(4)为开关导通与关断时的约束条件。在纹波系数为1‰时,有exp(一t1/1.2×10-8)≤0.001、exp(一t2/300)≥0.999,因此tl≥82.9 ns和t2≤300 ms。显然£l和t2不满足约束条件t2≥192t1,所以一轮开关切换不能同时满足式(2)和式(4)。为了提高精度,首先令t2300 ms,以满足式(4)条件。此时t1=1.56 ms。为了满足式(2),必需使Ui一Uo’足够小,经过计算,经1.56 ms时间电容可充到100%。

总之,要求如下:①开关切换最慢不低于192/t2≈640 Hz;②无论切换快慢,开关时间都要求大于192x82.9 ns=15.92μs,纹波才会小于1‰;③该采集系统的采样速率为500 Ks/s。

5 结语

由于整个系统的控制采用FPGA实现,具有组织方式灵活的特点,可以依据现场的具体情况,对FPGA的内部配置进行修改并调试。这种数据采集系统适用于多种数据采集的应用场合,是一种比较理想的实时数据采集方案。该设计已用于某装置信号的采集系统中。实际应用证明,该采集系统完全满足其多通道数据采集的要求。通过对典型单通道A/D采集系统的改进,在模拟开关级联的数据采集系统中。A/D转换器的输入端电容为多路开关的集成电容,其电容值较小。该改进方案提高了数据采集的速度和精度。

评论