基于FPGA的VGA显示控制器的设计

随着CCD(电荷耦合器件)和CMOS(互补金属氧化物半导体)图像传感器制造工艺的发展,图像传感器的分辨率越来越高,如果要实时显示图像传感器采集到的图像,则要求图像处理芯片有较高的运行速度,但由于需要处理的数据量太大,一般的数字信号处理器很难直接输出分辨率为1024×768,帧频为60 Hz的标准XGA信号。这就需要对DSP输出的图像数据进行处理,使图像能够在VGA显示器上实时显示。市场上虽然也有一些专门图像处理芯片,但其价格昂贵,且应用于特殊场合。本文设计的显示控制器可以达到提升帧频的功能,可使输入分辨率为1024×768,帧频为7.5HZ的YCbCr(4:2:2)图像信号提升到帧频为60HZ,并通过色空间转换,将YCbCr(4:2:2)图像信号转换成RGB格式的标准XGA信号,同时产生符合VESA标准的XGA格式的行、场同步信号,输出信号经D/A转换后可直接输出到VGA接口,从而可使图像传感器采集到的图像数据能够在VGA显示器上实时显示。

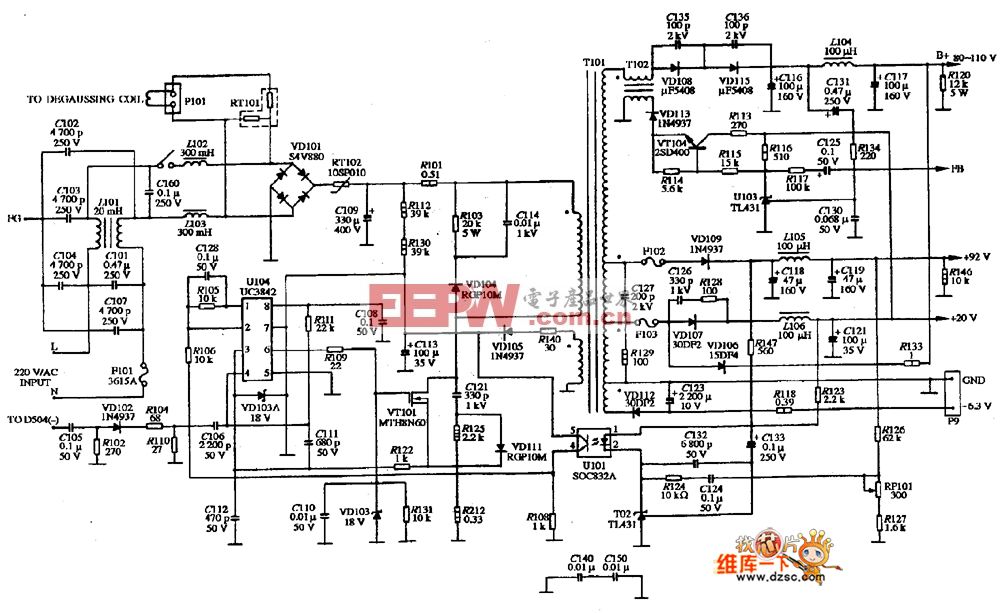

随着微电子技术及其制造工艺的发展,可编程逻辑器件的逻辑门密度越来越高,功能也越来越强,由于FPGA器件的可并行处理能力及其可重复在系统编程的灵活性,其应用越来越广泛。随着微处理器、专用逻辑器件、以及DSP算法以IP核的形式嵌入到FPGA中,FPGA可实现的功能越来越强,FPGA在现代电子系统设计中正发挥着越来越重要的作用。本文设计的显示控制器就是用VHDL语言描述,基于FPGA而实现的。该系统硬件框图如图1所示。

图1 系统硬件框图

1 显示控制器的设计

1.1 工作原理

图像传感器采集到的原始图像数据,经过A/D转换及DSP处理后,生成每秒7.5帧的图像数据,该数据是分辨率为1024×768的YCbCr(4:2:2)格式的16位图像数据。DSP输出到FPGA的信号有象素时钟,行、场参考,图像数据。FPGA在输入的行、场参考都有效时,在输入象素时钟的同步下,接收图像数据,并送入到SDRAM中, 同时从另一个SDRAM 中读取数据,并通过色空间转换,将YCbCr(4:2:2)信号转换成RGB信号。当SDRAM 中写满一帧图像数据时,控制器对两个SDRAM进行读、写切换。由于写数据速率小于读数据速率,所以在往一个SDRAM写满一帧图像数据的时间内,控制器能够连续多次从另一个SDRAM中读出另一帧图像数据,从而实现了提高帧频的目的。FPGA输出的RGB格式数据经D/A转换后,将数据转换成模拟信号,配合行、场同步信号可使其在VGA显示器上显示。外部晶振输入32.5MHZ的时钟,该时钟在FPGA内经时钟锁相环倍频后产生65MHZ的主时钟,用于对两个SDRAM进行读写和用来产生符合VESA标准的XGA格式的行、场同步信号。

1.2 控制器的内部模块介绍

本设计采用模块化设计原则,按照现代EDA工程常用的“自顶向下“的设计思想,进行功能分离并按层次设计,用VHDL语言实现每个模块的功能。该显示控制器主要由以下七个功能模块组成:

用于从DSP接收数据的输入缓冲模块

用于对两个SDRAM进行读写切换的主控制器模块

SDRAM1的控制器模块

SDRAM2的控制器模块

用于产生标准XGA格式的时序发生器模块

用于从SDRAM中读取数据并配合行、场同步输出数据的输出缓冲模块

用于将YCbCr(4:2:2)转换成RGB格式的色空间转换模块。

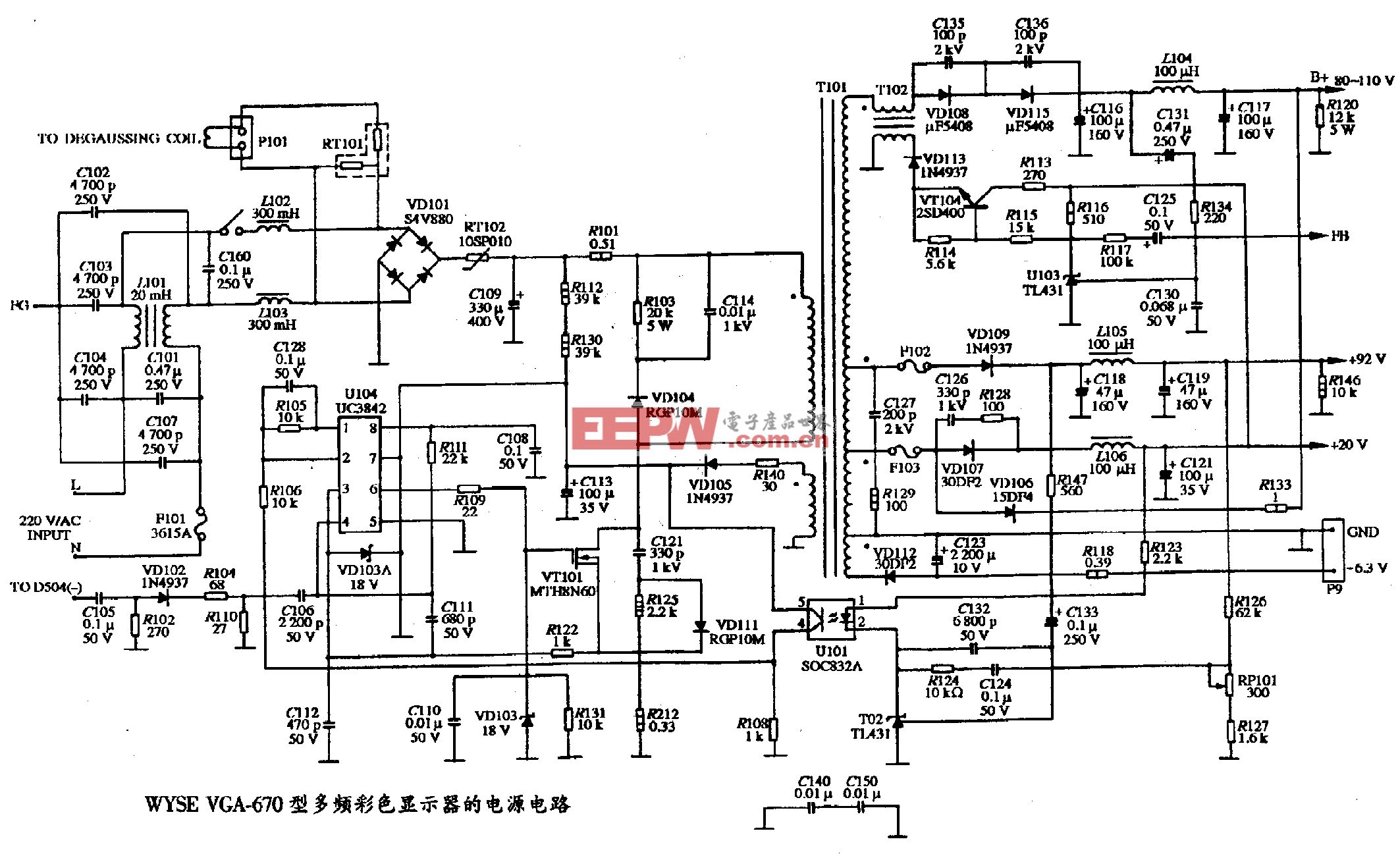

该显示控制器的内部结构如图2所示。上电后,显示控制器首先对两片SDRAM进行初始化,初始化结束后,其它模块才开始工作。下面将详细介绍各个模块的功能及设计思想。

图2 显示控制器的内部结构

评论