基于FPGA的数字解扩解调模块设计及实现

1引 言

本文引用地址:https://www.eepw.com.cn/article/192157.htm扩频通信系统是将基带信号的频谱扩展到很宽的频带上,然后进行传输,通过增大频带宽度来提高信噪比的一种系统。由于扩频系统具有抗干扰能力强、保密性高、截获概率低、多址复用和任意选址等优点,在移动通信等诸多领域越来越受到重视。

在扩频通信系统中,载波同步是扩频接收机正常解调的前提,是扩频通信中的一项关键性技术。常用的载波同步技术有平方环、Costas环和通用载波恢复环等。其中Costas环是跟踪低信噪比的抑制载波信号的最佳装置,也是现实中应用最多的一种。过去扩频信号载波同步常采用模拟Costas环,但是模拟环常存在I,Q通道间幅相不平衡、必须初始校准等问题。采用全数字实现的环路能够有效地避免这些问题。 本文介绍一种全数字Costas环,他能够很好地完成由BPSK调制的扩频信号的载波同步和跟踪,从而完成对调制信息的解扩解调。该电路具有可靠性高、体积小、功耗低、调试方便等优点。通过编程、综合和仿真,最后在FPGA上硬件实现本模块。测试结果表明,本模块的各项指标均达到设计要求。

2数字Costas环的基本原理

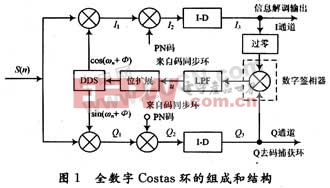

Costas环主要由数字下变频器、解扩单元、积分-清零器(I-D)、数字鉴相器、数字环路滤波器(LPF)以及数字控制振荡器(DDS)等模块组成。

当输入信号中扩频码(PN码)和来自码同步环的扩频码精确同步的情况下,输入信号通过解扩单元就可以去除扩频码,解扩后I,Q两路输出分别为:

当输入信号中扩频码(PN码)和来自码同步环的扩频码精确同步的情况下,输入信号通过解扩单元就可以去除扩频码,解扩后I,Q两路输出分别为

最后通过低通滤波器滤去二倍频,最终I,Q两路输出分别为:

可见,两路乘法器的输出均包含有调制信号,两者相乘可消除调制信号的影响,再经环路滤波器滤波后可得DDS控制电压:

由于DDS的控制电压已经去除了基带信号的成分,只受到相位误差φ的控制(k为常数),所以可以对DDS进行准确的调整,实现对载波的精确同步和跟踪。

3数字Costas环各子模块设计

在作者所参与的项目中,系统时钟fclk=48.96 MHz,载波频率为(12.24 M±1.5 k)Hz,数据速率fd=16 kb/s,A/D采样位数为8位。

3.1 DDS模块

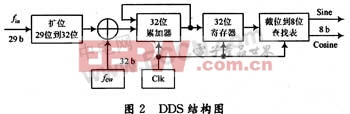

输人时钟:fclk=48.96 MHz;输出正弦:fo=12.24 MHz;DDS的位数:N=32 b。

从资源消耗和精度的综合考虑,采用了8位的查找表(IP核)来生成正弦余弦波,所以从累加器输出的相位信号必须截取高8位作为查找相位数据输入到查找表,输出正弦余弦信号也为8位。其具体实现结构如图2所示。

评论