基于FPGA的图像采集模块的设计

图像采集是图像处理的前提。图像采集卡是常用的图像输入设备,通常占用PC机总线的一个插槽。它主要包括图像存储器单元、CCD或CMOS摄像头接口、PC机总线接口等。传统的图像采集卡大多数采用PCI接口,这种图像采集卡适用于将模拟信号经A/D转换器转换成数字信号,或本身就是数字信号,再通过PCI接口传输至PC机,进行图像处理。但使用嵌入式系统实现图像采集和处理时,带有PCI接口的图像采集卡就不适用。为此,这里提出一种适用于嵌入式系统的数字图像采集模块设计方案,实现图像数据采集、“乒乓”模式图像数据的缓存、图像数据的采集模块外部接口,并保证图像采集的高速性和连续性。

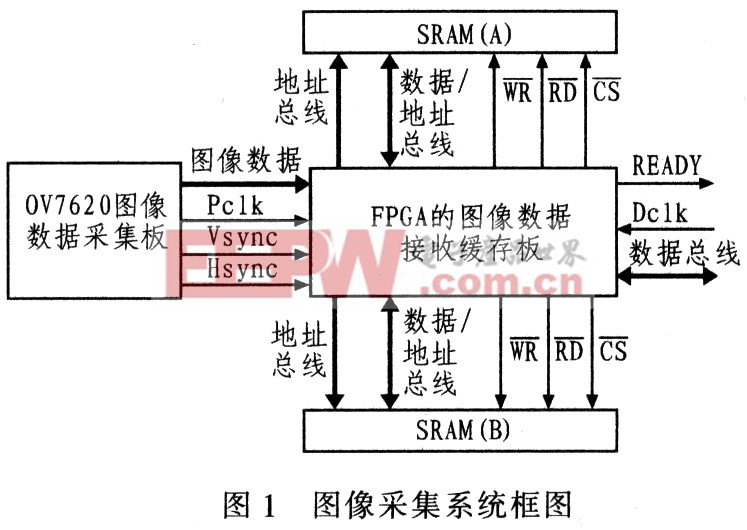

2 图像采集系统设计

图l为图像采集系统框图。该系统包括OV7620图像数据采集板、FPGA的图像数据接收缓存板、两片SRAM构成的高速缓存以及系统外部接口。OV7620图像数据采集板主要完成图像数据采集,其图像数据总线、帧图像数据时钟、帧同步信号、行同步信号与FPGA图像数据接收缓存板相连,FPGA协调两片SRAM“乒乓模式”的读写操作,并完成模块的外部接口。

2.1 OV7620图像数据采集板

数字图像采集模块的核心是图像传感器。OV7620内置640x480的图像阵列,每秒可输出30帧以上的图像;并集成有诸如曝光控制、伽马、增益、白色控制、彩色矩阵、彩色饱和度、色彩控制、窗口等照相功能。该器件能够通过串行SCCB接口编程,通过编程实现8位和16位格式的输出。

2.1.1 OV7620电路设计

该系统设计采用OV7620的电路如图2所示。其中,SBB引脚接跳线,用于设置OV7620在复位时读取引脚状态或I2C方式配置;UV2引脚接上拉电阻,选择0V7620为QVGA工作状态(320x240);Y3引脚接上拉电阻,选择OV7620为RGB数据格式输出:Y1引脚接上拉电阻,选择OV7620位逐行扫描模式;PWDN引脚接地,OV7620不能工作在睡眠模式;UV0~UV7,Y0~Y7,XCLKl,HSYNC,VSYNC,PCLK,HREF,FODD,FREX接26针的插座,与FPGA相连,由FPGA输出时钟和控制信号控制0V7620。在PCB设计时,应将模拟电源和数字电源、模拟地和数字地分开。电源的输入引脚接O.1μF的去耦电容和47μF的防止电源“浪涌”的电容。模拟地和数字地分开布线,最后在一点接地。晶体振荡器应尽可能靠近器件放置,使其起振效果达到最佳。

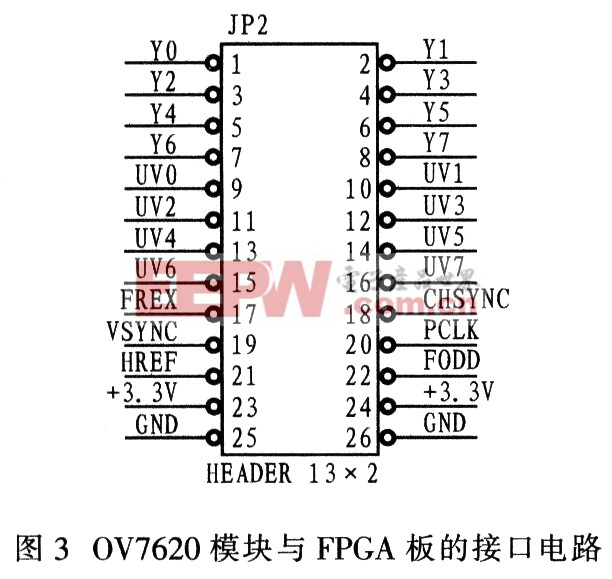

2.1.2 OV7620模块与FPGA板的连接

图3为0V7620模块与FPGA板的接口电路,其中3.3 V和GND是由FPGA板供电接口,UV0~UV7及Y0~Y7是图像数据的输出总线,VSYNC是图像帧同步信号,HREF是图像的行同步信号,PCLK是图像数据时钟在时钟的上升沿,图像数据发生跳变。

评论