基于SoPC的嵌入式语音处理系统的设计与实现

摘 要:介绍一种基于SoPC技术实现的语音处理系统的设计方法。系统主要由CyeloneⅡFPGA内嵌NiosⅡ软核处理器及音频编/解码芯片构成;通过构建嵌入式Linux操作系统来实现对音频信号的采集和回放处理。详细介绍通过SoPCBuilder配置NiosⅡ嵌入式处理器、外围设备及接口的过程,以及嵌入式Linux操作系统在SoPC系统上的移植过程。利用SoPC系统的可裁减性以及嵌入式系统的可移植性,可使该设计作为一个子系统应用在如网络会议的视频电话中,该方法对SoPC系统的开发研究具有较高的参考价值。

关键词:片上系统;嵌入式Linux;音频编码;音频解码;软核处理器

0 引 言

可编程的片上系统(System on PrograromableChip,SoPC)是现代计算机辅助设计技术、EDA技术和大规模集成电路技术高度发展的产物。它可以将处理器、存储器、I/O接口、硬件协处理器和普通的用户逻辑等系统设计需要的功能模块都集成到1片FPGA芯片内部,实现MCU,DSP和FPGA的完美结合,这将是未来嵌入式系统的发展趋势,在仪器仪表、手持设备上有着广阔的应用前景。

在此利用SoPC技术设计了语音处理系统,包括语音的采集和回放处理,该系统可以作为音视频监控系统、VoIP等系统的语音处理模块。

1 系统构成方案

1.1 系统硬件构成

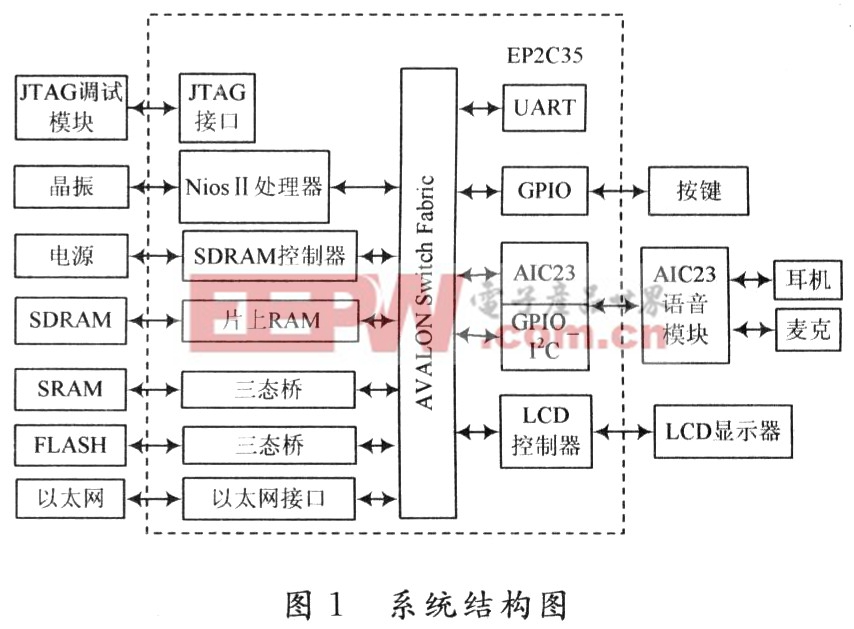

设计的嵌入式语音处理系统的硬件结构如图1所示。系统的主控部分由CycloneⅡEP2C35系列FPGA芯片、外围电路及语音编解码芯片构成。EP2C35是Altera公司推出低成本FPGA芯片,该芯片具有33 216个逻辑单元(LE)、105个M4KB RAM块、RAM总位数是483 840 b、4个锁相环和35个嵌入式乘法器以及丰富外部扩展引脚。

CycloneⅡ系列FPGA片内结构是以32 b NiosⅡ处理器作为核心,NiosⅡ处理器是AItera公司的第二代用户可配置的、采用流水线技术、单指令流的32位RISC内嵌处理器,基于通用FPGA架构的软CPU内核,其性能超过200 DMIPS。NiosⅡ处理器内核有3种类型,分别是快速型、经济型和标准型,用来满足不同的设计要求。

音频部分主要由语音编解码芯片TLV320AIC23和外部输入/输出器件构成;通过麦克风采集模拟音频信号,经过AIC23转换为数字音频信号,由NiosⅡ处理器进行语音的存储及传输;NiosⅡ处理器输出的数字音频信号经过AIC23转换为模拟音频信号,通过耳机播放。系统内部包括UART,以太网接口等可以方便地实现系统的扩展,实现诸如IP电话的系统设计。

1.2 主控芯片FPGA的配置

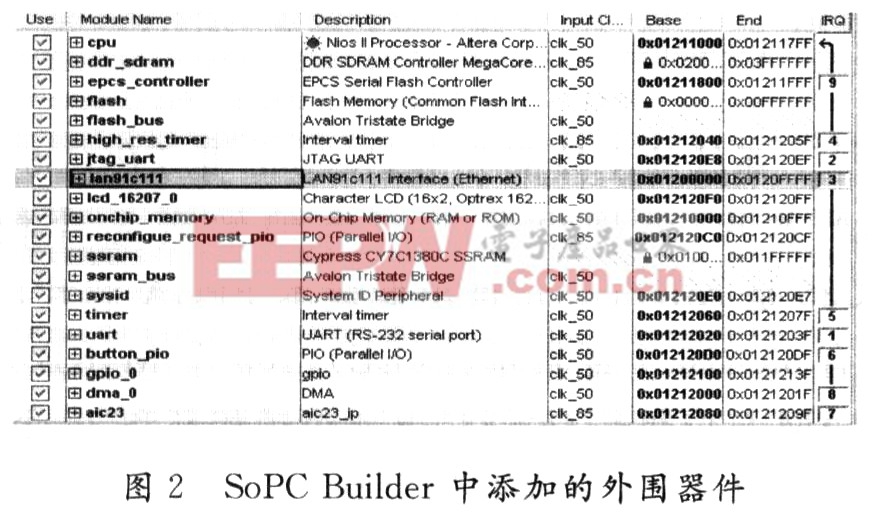

主控芯片FPGA的配置是通过SoPC Builder在CycloneⅡFPGA开发平台上实现的。根据需求,该系统主要配置如下:标准型NiosⅡ处理器、片上SDRAMMT46V16M16、以太网芯片LAN91C111,FLASH存储器件AM29LVl28M,SSRAM器件CY7C1380C,UART,JTAG UART,PLL锁相环、定时器Timer,DMA,I2C,AIC23等控制器核。其中以太网芯片、FLASH存储器件、SSRAM器件通过Avalon三态总线桥与Avalon Switch Fabric连接,所有的外围接口通过AvaIon Switch Fabric与NiosⅡ处理器连接。通过SoPC Builder添加的主要外围接口如图2所示。

系统添加外围器件的控制核后,经过SoPC Builder定义生成系统,集成SoPC Builder系统到QuartusⅡ工程,进行引脚分配,编译硬件设计,生成配置文件.sof和.ptf文件。SoPC Builder是一个自动化的系统开发工具,能够非常容易地在一个设计中加入NiosⅡ处理器以及其它外设接口。

2 系统接口设计

系统主要模块在FPGA片内生成,外部接口主要是TLV320AIC23与CycloneⅡEP2C35的硬件接口设计。

TLV320AIC23(AI(223)是TI公司的一款高性能的立体声音频编解码器,设计中通过其自带的A/D,D/A转换器来完成模拟音频信号的采样和数字音频信号的D/A转换工作;AIC23中的模/数与数/模转换器使用了多比特sigma―delta工艺,并在内部集成了高采样率的数字内插滤波器。该器件的数字传输字长可以是16,20,24,32 b,它支持8~96 kHz的采样率。AIC23内部有11个配置寄存器,可通过控制接口来配置该器件的寄存器,AIC23的控制接口有SPI,I2C两种规格。模式终端状态决定了控制接口的形式,在设计中MODE接数字地表示利用I2C控制接口对AIC23传输控制数据。I2C总线是Philips公司开发的一种双向两线多主机总线,它能方便地实现芯片间的数据传输与控制。CS接数字地定义了在I2C总线上A IC23的7 b外设地址为“0011010”。该系统的I2C接口使用GPIO一I2C,即用2根通用的I/O口作为I2C时钟线SCL和数据传输线SDA,通过软件实现I2C协议。

AIC23芯片与数字系统的接口有右判断模式、左判断模式、I2S模式和DSP模式4种。设计中使用I2S数据传送模式。I2S总线是飞利浦公司为数字音频设备之间的音频数据传输而制定的一种总线标准,广泛应用于各种多媒体系统。数字音频接口由时钟信号BCLK、数据信号DIN和DOUT、同步信号LRCIN和LRCOUT组成。应当说明:BCLK在主动方式下是输出,而在从动方式下是输入。AIC23的IP核包I2S发送/接收模块、输入/输出FIFO存储器模块,AIC23的IP核结构如图3所示。

评论