一种基于FPGA的PXA270外设时序转换接口设计

1 引言

ARCNET协议应用于高速动车组列车通信网络时,产生中央控制单元处理器PXA270与专用协议控制器件COM20020相连的时序不匹配问题,若用通用数字电路模块进行时序转换,PXA270需占用PXA270专门的资源(CPU时间片)对 COM20020的寄存器、数据包缓冲区进行低速读写访问(对COM20020的相邻两次读操作相隔至少300 ns),这样将增加处理器的负担。基于这种现状,提出一种基于FPGA的PXA270外设时序转换接口设计方案,以FPGA为桥梁进行时序转换,并增加存储器直接访问DMA(Direct Memory Aeeess)功能,即FPGA自动完成数据包的收发工作,PXA270则只需高速读写访问FPGA中的同步双口RAM。

2 时序转换接口整体设计

2.1 FPGA对外接白

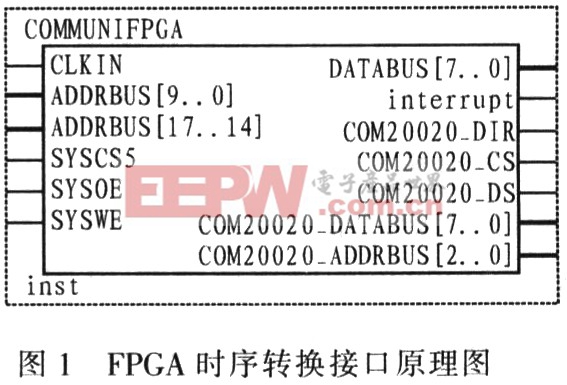

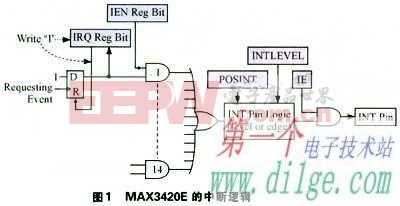

采用FPGA连接PXA270处理器与外设以解决PXA270处理器与外设直接连接时的时序不匹配问题。如图1所示,FPGA从PXA270处理器获得地址总线(ADDRBUS[17..14], ADDRBUS[9..0]),片选信号(SYSCS5),读允许(SYSOE),写允许(SYSWE),并提供双向数据端口DATABUS[7..0] (可根据实际应用修改为32位或16位等),中断(interrupt);同时,FPGA向COM20020提供特定的总线接口,包括 COM20020_DS,COM20020_CS,COM20020_DIR,COM20020_DATABUS [7..0],COM20020_ADDRBUS[2..0]等。

2.2 内部功能实现

PXA270和外设之间的连接是将FPGA中的双口RAM作为数据中转站,以此间接相连。该设计由以下4个功能模块组成。

(1)PXA270对外设指定寄存器单次写操作PXA270先将所要写的数据送人双口RAM,然后PXA270向FPGA的命令寄存器写入对该外设指定寄存器的单次写指令,然后FP-GA根据接收到的命令将RAM中的数据输出到外设数据总线,同时给出对外设的写时序。

评论