基于ASIC设计的手工综合研究

随着专用集成电路(Application Specific Integrat-ed Circuit)设计的迅速发展,将寄存器传输级(RTL)描述的手工综合成门级网表,是IC前端设计中的关键技术。在当前IC设计中,通常在行为级功能验证后,采用软件进行自动综合的方式。这种方式虽然缩短了ASIC设计的周期,但是利用软件综合的门级电路存在很大的冗余,从而影响到整个芯片的版图面积和延时。如果采用手工综合,则会得到最简的电路结构和最少的线路延时。在总体上,手工逻辑综合可分为时序逻辑综合和组合逻辑综合。

在此,以成功开发的无线发码遥控编码芯片为实例,详细介绍手工综合RTL级代码的理论依据和实用方法,重点介绍时序逻辑综合的实现方法,将时序逻辑综合的实现方法归纳出各种描述的一般特征,将用户多种多样的描述归整为五种形式,避免了综合过程中的盲目性,使得整个综合过程有据可依,从而提高综合的效率和准确性,并对手工综合进行深入的研究。

1 组合逻辑综合

组合逻辑综合的功能是对组合逻辑函数的描述形式进行一系列转换和优化,求取实现该逻辑函数性能最佳的组合逻辑结构形式,并生成与逻辑功能描述相等价的优化的逻辑级结构描述。由于行为级描述或寄存器传输级描述经转换后所得到的逻辑级的逻辑函数表示通常都是非优化的表示,因此就需要使用逻辑优化工具对其进行综合和优化。

组合逻辑综合的目标通常有:其一是为了在满足延迟的约束下将面积最小化;其二是为了提高电路的可测试性。

组合逻辑电路设计是数字电路设计的基础。相对时序逻辑电路而言其综合过程要简单,可参考上面的手工综合步骤,在这里设计了两个电路对ASIC的手工综合进行具体研究。

1.1 单增量加法器(4位)

所谓单增量加法器,就是在二进制计算中,行使代码换算的任务,即二进制计算中若输出有N值存在,接下来的数值就是N+1,为了把输出值从N变为N+1就必须做一个电路。若其Verilog HDL描述语言为:

counter_disp=counter_disp+4'd1;

则综合步骤为:

(1)列出真值表(略);

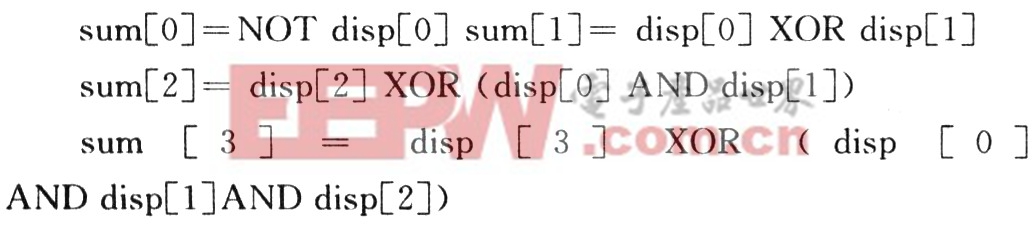

(2)从真值表可以得出其逻辑表达式为:

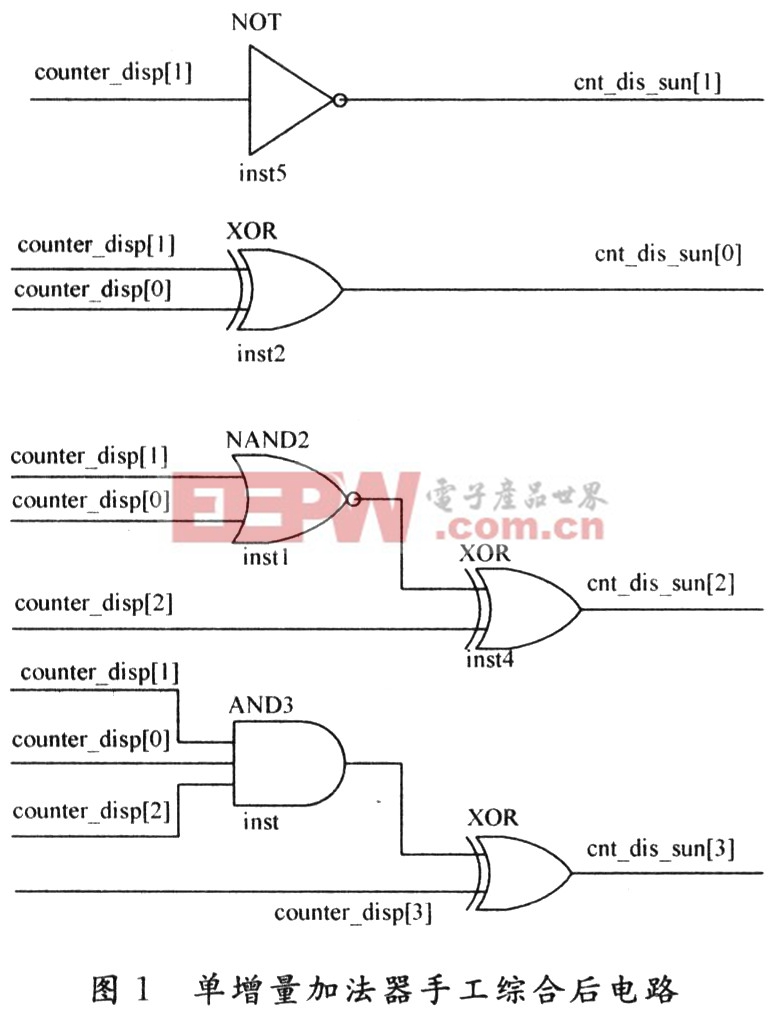

(3)综合后的电路图如图1所示。

评论