基于ASIC设计的手工综合研究

2 时序逻辑综合

时序逻辑综合的主要研究集中于同步时序电路的设计综合。异步时序电路由于其设计和控制过程的复杂性,自动综合十分困难。同步时序电路逻辑综合研究的内容主要有:同步时序电路的综合方法(即有限状态机的综合)、时序的优化以及时钟系统的设计优化等。有限状态机综合的主要任务是根据给定的逻辑功能,选取触发器和锁存器等时序元件,寻求优化的时序状态激励函数。同步时序电路综合的目标是获得芯片面积优化的高性能电路结构形式,其中包括时序重构和时序逻辑优化等方面。时序优化与时钟系统的优化通过分析时序电路的数据传输行为,设置合理的参数,提高系统的效率,消除时序错误,解决时序冲突。优化电路,得到最终的门级电路网表。

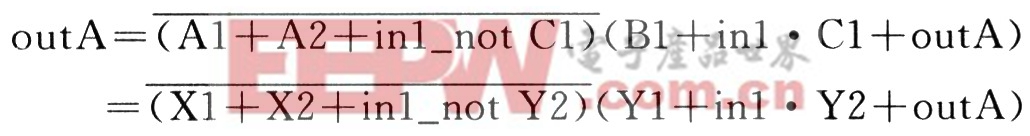

在进行了格式判别,确定采用何种时序元件后,就可以从相应的目标库中提取相应的元件,组织成符合最终输出形式的网表格式。在提取元件时应当根据用户的输入描述取得最优化的结果,当然,这种优化问题也可以在得到最终的数据通道之后进行。对于同步/异步复位及上升/下降沿触发的问题,在一般的目标库中,都有各种不同类型的时序逻辑电路元件,同步/异步复位元件为其中之一。同步/异步复位触发器的综合与其他元件的综合有所不同,综合时考虑的不仅是某一条赋值语句,而是将用户的描述作为一个整体来考虑。在提取赋值语句时,同时分析相互有关联的语句以及这些语句的相关条件,根据上下文语义得出最终的结论。下面针对上述理论用一实例来说明:在采用上面的综合步骤预处理和综合实现算法后,得到输出信号outA的赋值情况如下:

条件X1成立时outA≤0;条件X2成立时outA≤0;条件Y1成立时outA≤1;条件Y2成立时OutA≤in1;其他条件下outA保持。

其处理过程如下:

(1)将所有使输出信号为0的条件标识为A1,A2等A类(A1=X1,A2=X2);

(2)将所有使输出信号为1的条件标识为B1,B2等B类(B1=Y1);

(3)将所有使输出信号为某个输入信号或中间信号值的条件标识为C1,C2等C类(C1=Y2);

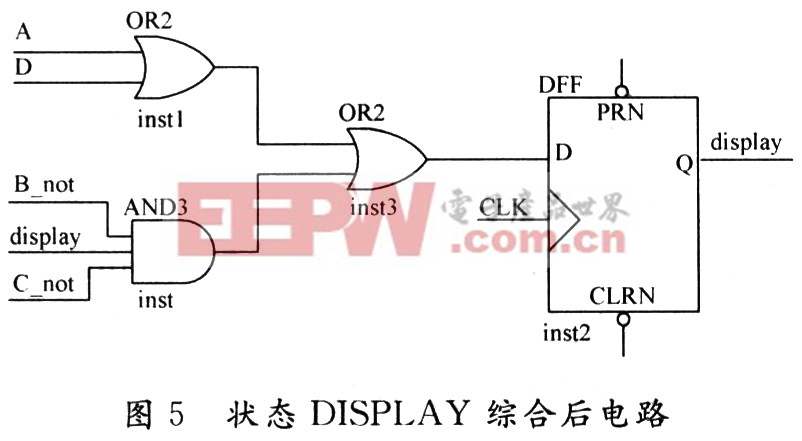

(4)写出其逻辑表达式:

(5)将目标信号的逻辑表达式进行画简(这里设定已为最简式);

(6)画出对应的逻辑电路图(见图3):(其中in1_not表示为in1的非,其余类同。)

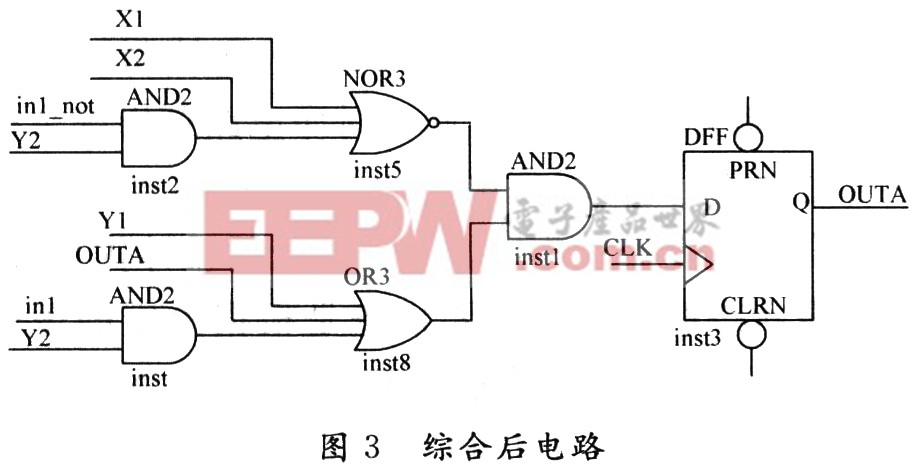

具有数据通道的有限状态机是描述数字系统的最常用的模型。有限状态机分为两个部分:数据通道部分和控制部件部分。数据通道部分包括数据的处理部件、存储部件、传输部件及其互连。控制部分主要完成数据通道的时序控制,以及根据当前状态、外部控制输入和数据通道内部状态产生外部控制输出和数据通道控制信号等。逻辑综合接受算法级行为描述,通过将其编译转换成为内部表示形式,然后经过操作调度和硬件资源分配等处理过程,最终产生表示数据通道的寄存器传输级网表,并根据调度的需要提取控制信息产生控制部件的行为描述(即有限状态机的描述,一般为状态转换表/图)。控制流综合对行为描述的有限状态机进行分解、化简、分配等处理,选取时序元件,导出状态转换函数和控制输出函数。

下面以一个实例来介绍控制部分的逻辑综合过程和方法。按照前面的步骤,分析Verilog HDL代码,已得出该控制流部分的状态转换图(见图4),在这里只列出用符号代替的状态转移条件,未写出各输出端信号。

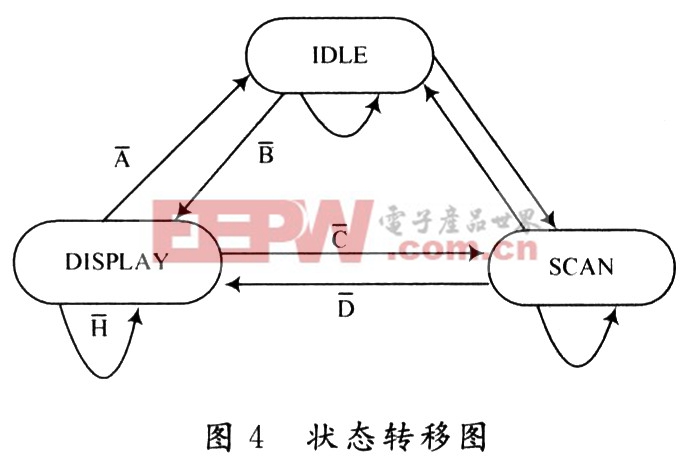

这是IED驱动控制芯片核心模块(显示和键扫控制模块)的状态转换图,下面以DISPLAY状态为目标求其状态转移电路图,如图5所示。

(1)根据状态转移图列出与DISPLAY状态相关的状态转换条件:

当A=1,DISPLAY=1 D=1时,DISPLAY=1;

当B=1,DISPLAY=0 C=1时,DISPLAY=0

(2)推断出DISPLAY状态保持的条件,设为E:E=(BDISPLAY)||(CDISPLAY)+H=BC&&DISPLAY+H=BC&&DISPLAY

(3)化简并得出DISPLAY的逻辑表达式:

DISPLAY≤A+D+E

(4)画出其逻辑电路图(状态机采用独热码编码方式)。

3 结 语

在此归纳出一套手工逻辑综合的方法和综合步骤,该方法适用于中小规模和超大规模中的核心电路部分的电路综合。同时手工综合后的效果与自动综合软件相比,其电路可靠且使用的门电路规模减少,功耗降低,延时达到最小。

评论