针对噪声模拟设计的 ASIC 修复

噪声是混合信号 ASIC 中的一个常见问题,会降低性能并危及产品的完成度。本应用笔记提供了添加外部电路的提示和技巧,使许多 ASIC 可用于原型设计或作为终产品进行交付。讨论了通过校正模拟电路中的噪声、进行调整、校准增益和偏移以及清洁电源来优化 ASIC 的方法。其回报是更快的上市时间,甚至可以防止额外的 ASIC 制造旋转。

本文引用地址:http://www.eepw.com.cn/article/202309/450192.htm噪声是混合信号 ASIC 中的一个常见问题,会降低性能并危及产品的完成度。本应用笔记提供了添加外部电路的提示和技巧,使许多 ASIC 可用于原型设计或作为终产品进行交付。讨论了通过校正模拟电路中的噪声、进行调整、校准增益和偏移以及清洁电源来优化 ASIC 的方法。其回报是更快的上市时间,甚至可以防止额外的 ASIC 制造旋转。

简介

本应用笔记解决了模拟设计中常见的缺陷,即噪声。它讨论了针对墨菲定律在预定 ASIC 生产中出现的问题的一些解决方案。此外,还建议了一些步骤或程序来帮助工作设计师和工程师解决常见的设计问题。

噪声是混合信号 ASIC 中的一个常见问题,会降低性能并危及产品的完成度。本应用笔记提供了添加外部电路的提示和技巧,使许多 ASIC 可用于原型设计或作为终产品进行交付。讨论了通过校正模拟电路中的噪声、进行调整、校准增益和偏移以及清洁电源来优化 ASIC 的方法。其回报是更快的上市时间,甚至可以防止额外的 ASIC 制造旋转。

的专用集成电路 (ASIC) 的首片成功率超过 90%。您可能想知道为什么我们要讨论“解决”这个问题的方法?毕竟,ASIC 几乎可以工作了,没有时间旋转它并仍然满足市场窗口的要求。听起来有点熟?不幸的是,墨菲定律1 说:“任何可能出错的事情,都会在糟糕的时候出错”,这也适用于此。无论我们如何模拟、构建现场可编程门阵列(FPGA)和原型,都会有惊喜。小事情需要改进。然后,正当你认为自己已经接近目标时,销售人员却表示,如果没有其他“小”功能,他们就无法销售该设备。当然,引进的期限不能延长。这种戏剧并不陌生,它可能是 ASIC 设计师的噩梦。

我们经常在 ASIC 上看到模拟设计错误。我们拿起一块板,在角落里有一个“哎呀逻辑”,这个设计功能在当时看来是正确的,但现在显然不起作用了。本文讨论解决“哎呀”问题的方法。我们提供了添加外部电路的提示和技巧,以使许多 ASIC 可用于原型设计,或者在许多情况下可用于可交付的产品。我们展示了如何校正模拟电路中的噪声、进行调整、校准增益和偏移以及清洁电源。回报是每个人的目标:更快的上市时间,甚至避免额外的 ASIC 制造旋转。

优化模拟以降低噪声

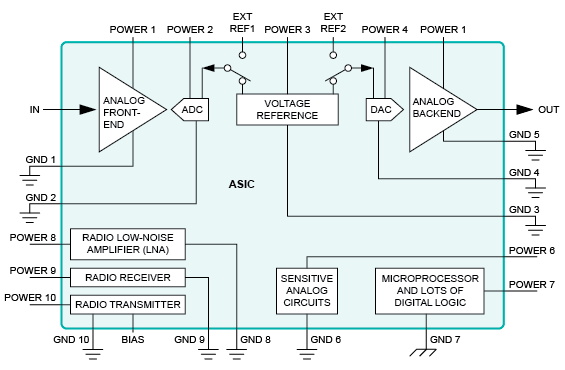

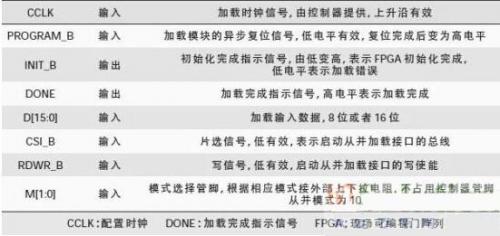

噪声是混合信号 ASIC 中的一个常见问题,主要是因为数字逻辑开关噪声会进入敏感的模拟电路。图 1 显示了情况布局,其中每个模块都有自己的电源和接地引脚。尽管如此,数字电路正在以快速边沿切换电流,从而对接地和电源引脚产生串扰和反弹。

如果同一封装中有两个芯片(一个模拟芯片和一个数字芯片),并且构建方式非常类似于混合芯片,则这种布局将是理想的。该配置将允许两个真正独立的接地,因为电路不会共享公共硅基板。唉,在现实世界中,这个 ASIC 是一个芯片,但拥有尽可能多的独立电源和接地引脚仍然很重要。这为我们排除故障和解决问题时提供了的灵活性。现在让我们看看优化该电路中某些模块的方法。

微处理器和数字逻辑中的开关噪声

我们从右下角开始检查图 1 电路,即微处理器和其他数字逻辑,它们都是开关噪声的来源。缺乏经验的设计人员可能会说,“但时钟只有 1MHz。” 这是事实,但完美方波的边缘具有延伸至无穷大的奇次谐波。实际上,多的能量是在前五到七个谐波中。同样在时钟系统中,时钟使除传播延迟之外的边沿一致。,CMOS 输出在开关期间消耗电流。

图2显示了电流的两种用途:一是给下的电容充电;二是给后级电容充电。第二,在开关期间为两个晶体管部分供电。请参见图 3 中的数据。虽然电流很小,但当有数百万个晶体管进行开关时,电流就会累积起来。

ASIC 修复嘈杂的模拟“Oops”_2.png

这会给我们带来什么?一些设计人员使用术语“模拟”和“数字”来区分电源域和接地域。我们分别更喜欢“干净”和“肮脏”这两个词,因为它有助于思考过程。在 ASIC 内部,接地可能会反弹,从而将数字接地噪声引入模拟电路。因此,这两个接地域需要在一个系统星点处连接,以保持噪声分离。选择电源去耦电容器时需要考虑电容器的自谐振。数字逻辑中的阈值可消除噪声,而模拟电路则没有阈值。

提高 ADC 的 SNR

现在转向为 ADC 供电的模拟前端 (AFE)。它由多路复用器、放大器和滤波器组成。如果 ADC 信号有噪声,我们会查看输入信号的信噪比 (SNR),以确定可以改进的地方。有几个简单的问题需要问。是否使用了 ADC 的全部范围?我们可以使用放大器和数字电位器添加增益或偏移来居中并优化信号范围吗如果输入信号噪声太大,我们可以清理源的电源,甚至使用低噪声基准来为其供电吗?是否存在带外 (OOB) 射频干扰 (RFI) 或电磁干扰 (EMI)?我们可以屏蔽电路、添加双绞线、使用差分输入放大器或添加低通滤波器来消除共模噪声吗?5,6 这些问题的简短答案是,是的。

另一个常见问题是 AFE 的信号源。假设传感器不可用或需要更换为其他制造商的部件。情况变得更加复杂,因为替换部件可能具有不同的输出质量;它可能需要使用外部放大器进行阻抗变换、增益或偏移才能继续进行类似操作。AFE 本身的噪音可能太大,那么我们能否通过串联电感器、电阻器或铁氧体磁珠更好地实现电源去耦?低噪声基准电压源也可以用作电源替代品。

结论

我们可以通过不需要再次完整布局的简单修复来解决多少其他 ASIC 问题?在我们看到它们并尝试之前,我们永远不会知道。工程师们知道,墨菲和他的“定律”始终潜伏在设计实验室的阴影中。这就是为什么每个智能 ASIC 设计人员都需要经验丰富的模拟工程师来预测问题并解决影响产品上市时间的模拟噪声问题(“oops”)。

评论