基于CPLD/FPGA的多功能分频器的设计与实现

引言

本文引用地址:https://www.eepw.com.cn/article/191883.htm分频器在CPLD/FPGA设计中使用频率比较高,尽管目前大部分设计中采用芯片厂家集成的锁相环资源 ,但是对于要求奇数倍分频(如3、5等)、小数倍(如2.5、3.5等)分频、占空比50%的应用场合却往往不能满足要求。硬件工程师希望有一种灵活的设计方法,根据需要,在实验室就能设计分频器并马上投入使用,更改频率时无需改动原器件或电路板,只需重新编程,在数分钟内即可完成。为此本文基于 CPLD/FPGA用原理图和VHDL语言混合设计实现了一多功能通用分频器。

分频原理

偶数倍(2N)分频

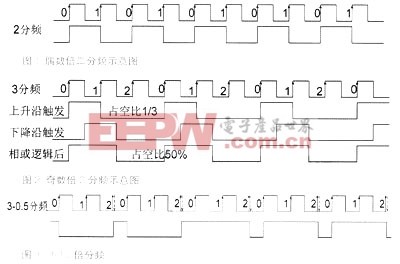

使用一模N计数器模块即可实现,即每当模N计数器上升沿从0开始计数至N时,输出时钟进行翻转,同时给计数器一复位信号使之从0开始重新计数,以此循环即可。偶数倍分频原理示意图见图1。

奇数倍(2N+1)分频

(1)占空比为X/(2N+1)或(2N+1-X)/(2N+1)分频,用模(2N+1)计数器模块可以实现。取0至2N之间一数值X(0 X2N),当计数器时钟上升沿从0开始计数到X值时输出时钟翻转一次,在计数器继续计数达到2N+1时,输出时钟再次翻转并对计数器置一复位信号,使之从0开始重新计数,即可实现。

(2)占空比为50%的分频,设计思想如下:基于(1)中占空比为非50%的输出时钟在输入时钟的上升沿触发翻转;若在同一个输入时钟周期内,此计数器的两次输出时钟翻转分别在与(1)中对应的下降沿触发翻转,输出的时钟与(1)中输出的时钟进行逻辑或,即可得到占空比为50%的奇数倍分频时钟。当然其输出端再与偶数倍分频器串接则可以实现偶数倍分频。奇数倍分频原理示意图见图2。

N-0.5倍分频

采用模N计数器可以实现。具体如下:计数器从0开始上升沿计数,计数达到N-1上升沿时,输出时钟需翻转,由于分频值为N-0.5,所以在时钟翻转后经历 0.5个周期时,计数器输出时钟必须进行再次翻转,即当CLK为下降沿时计数器的输入端应为上升沿脉冲,使计数器计数达到N而复位为0重新开始计数同时输出时钟翻转。这个过程所要做的就是对CLK进行适当的变换,使之送给计数器的触发时钟每经历N-0.5个周期就翻转一次。N-0.5倍:取N=3,分频原理示意图见图3。

对于任意的N+A/B倍分频(N、A、B∈Z,AQB)

分别设计一个分频值为N和分频值N+1的整数分频器,采用脉冲计数来控制单位时间内两个分频器出现的次数,从而获得所需要的小数分频值。可以采取如下方法来计算个子出现的频率:

设N出现的频率为a,则N×a+(N+1)×(B-a)=N×B+A 求解a=B-A; 所以N+1出现的频率为A.例如实现7+2/5分频,取a为3,即7×3+8×2就可以实现。但是由于这种小数分频输出的时钟脉冲抖动很大,现实中很少使用,本次设计未予以设计。

分频器相关文章:分频器原理

评论