基于FPGA的高速数字相关器设计

摘要:在数字通信的数据传输过程中,需要保持数据在传输过程中的同步,因此要在数据传输过程中插入帧同步字进行检测,从而有效避免发送数据和接收数据在传输过程中出现的异步问题。文中提出了一种采用流水线技术、基于 FPGA设计高速数字相关器的方法。仿真结果表明设计方案是可行的。

本文引用地址:https://www.eepw.com.cn/article/191861.htm在数字通信系统中,常用一个特定的序列作为数据开始的标志,称为帧同步字。在数字传输的过程中,发送端要在发送数据之前插入帧同步字。接收机需要在已解调的数据流中搜寻帧同步字,以确定帧的位置和帧定时信息。帧同步字一般为一系列连续的码元,在接收端需要对这一系列连续的码元进行检测,如果与预先确定的帧同步字吻合,则说明接收端与发送端的数据是保持同步的,开始接收,否则不能进行接收。完成帧同步字检测工作的正是数字相关器。本文采用流水线技术,研究了基于 FPGA的高速数字相关器的设计方法,并给出了 MAX+PLUSII环境下的仿真结果。

1 数字相关器原理

数字相关器在通信信号处理中实质是起到数字匹配滤波器的作用,它可对特定码序列进行相关处理,从而完成信号的解码,恢复出传送的信息。其实现方法是进行两个数字信号之间的相关运算,即比较等长度的两个数字序列之间有多少位相同,多少位不同。昀基本的相关器是异或门,例如,y=ab,当 a=b时,y=0,表示两位数据相同;当 a≠b时,y=1,表示两位数据不同。多位数字相关器可以由一位相关器级连构成。 N位数字相关器的运算通常可以分解为以下两个步骤:对应位进行异或运算,得到 N个 1位相关运算结果;统计 N位相关运算结果中 0或 1的数目,得到 N位数字中相同位和不同位的数目。

当数字相关器接收到一组数据时,在时钟的上升沿对帧同步字进行检测。对于帧同步字是一个连续 16位的码元,数字相关器在进行检测的过程中,只有当连续检测到 16位的码元与预先设定的帧同步字完全相同时,才由输出端输出信号表示帧同步。否则,任何一位出现不相等,数字相关器又将重新开始进行检测,直到出现连续的 16位码元与预先设定的 16位码元完全相等时才进行输出。数字相关器的设计一般考虑采用串行输入或并行输入两种输入检测方式,由于串行输入是在 16个时钟周期内依次对两路串行输入信号 A、B进行异或运算,并统计数据位相同个数,检测速度较慢,要提高检测速度,就要考虑采用并行输入检测方式。

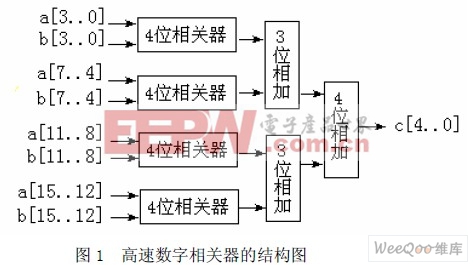

在 16位并行数字相关器中,由于实现 16位并行相关器需要的乘积项、或门过多,因此为降低耗用资源,可以分解为 4个 4位相关器,然后用两级加法器相加得到全部 16位的相关结果,其结构图如图 1所示,如果直接实现该电路,整个运算至少要经过三级门延时。随着相关数目的增加,速度还将进一步降低。为提高速度,采用“流水线技术”进行设计,模块中对每一步运算结果都进行锁存,按照时钟节拍逐级完成运算的全过程。虽然每组输入值需要经过三个节拍后才能得到运算结果,但是,每个节拍都有一组新值输入到第一级运算电路,每级运算电路上都有一组数据同时进行运算,所以总的来讲,每步运算花费的时间只有一个时钟周期,从而使系统工作速度基本等于时钟工作频率。

评论