基于DSP和FPGA的实时图像压缩系统设计

1 系统工作原理及硬件设计

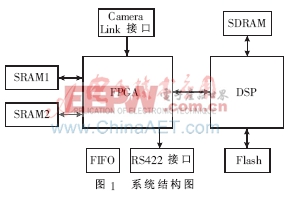

系统由Camera Link接口模块、以FPGA为核心的图像采集预处理与传输单元、以DSP为核心的图像压缩单元以及RS422远距离数据传输单元组成。由于采集、处理均需要访问存储器,为了降低成本,采用普通的异步SRAM,按功能区分可分为采集SRAM和压缩处理SRAM。读写逻辑由FPGA控制,采用乒乓机制进行切换。整个系统结构如图1所示。

系统工作过程:图像信号经由LVDS转换芯片后转换成LVTTL信号,直接传送至FPGA解码为8位数据,以字节方式一行一行写入SRAM静态存储器(存储器由两部分组成),用于乒乓缓存输入数据,每部分满1帧后由FPGA控制送出帧中断给DSP,DSP启动EDMA读入1帧数据,采用JPEG2000方式编码后连续写入到FIFO_OUT,FPGA负责从FIFO_OUT读出数据,非空即读,缓存积累不会超过1帧数据。读出的数据另行打包后以9 Mb/s的码率通过DS26LV31 422接口芯片从out1接口输出,或者分流后从out1和out2以各4.5 Mb/s的码率输出。

2 FPGA功能模块设计

2.1 Camera Link接口模块

Camera Link接口模块负责对高频帧数字摄像头输出的LVDS信号转换为TTL标准信号。

关于Camera Link的采集数据的逻辑代码,关键之处在于产生存储器的地址信号、存储器写信号以及在对应的地址处将数据稳定地写进存储器。本系统用像素时钟产生列地址计数器、行同步信号产生行地址计数器,两者拼接产生存储器的地址信号。这样产生的有效地址虽然不连续,但意义明确,而且有利于显示部分的隔行隔列显示。对于8 bit的数据,可将2个有效数据拼接成16 bit后再存储,这样可以提高FPGA读写存储器的速度。

Camera Link接口时序如图2所示。

图2中:VD为帧同步信号,电平模式,高电平有效;HD为行同步信号,脉冲模式,上升沿有效;PCLK为像素同步时钟,脉冲模式;DATA为10 bit图像数据,在PCLK的下降沿推出,接收端在PCLK上升沿采集,PCLK为常运行模式。每个VD有效期内有480个HD有效信号,在第0~478个HD有效时,每个HD有效期间有600个有效图像数据,第479个HD(即每帧的最后1行)有效时,前600个DATA为有效图像数据,600个DATA后预留6个字节输出图像相关信息,即第D600~D605为预留字节。

2.2 SRAM乒乓缓存

在图像采集处理系统中,DSP的压缩算法在实现时间上往往并不是固定不变的,然而前端的采集模块却使用均匀速度对图像进行采集,这样存在时间上的不同步,有可能会导致图像数据的丢失和影响帧数据的完整性[2]。为此,本系统在采集和压缩模块之间增加1个缓冲电路来解决这一问题。

常用的缓冲电路主要有3种[3]:双口RAM结构、FIFO结构和乒乓结构。由于乒乓结构可以使用相对比较便宜的高速大容量SRAM,而且可以实现数据的连续性,因此本系统采用了乒乓结构双SRAM作为视频数据的缓冲。在将1帧图像的数据全部存储完以后,DSP再利用很短的时间直接将1帧图像数据读入片内,这样既可以保证不丢失像素数据、DSP可以连续采集每1帧像素数据,又能为DSP留出更多空余时间,为后面进行图像处理提供可能。为了实现数据帧的完整性,必须保证读取数据帧的优先级要高于写数据帧的优先级,所以本系统的数据输入输出单元是根据数据处理流程来进行切换的。

评论