基于模块化设计方法实现FPGA动态部分重构

关键词:FPGA;动态部分重构;重构;Virtex

随着可编程技术的不断发展,FPGA被广泛应用于电子设计的各个领域。新的设计思想和设计方法也被不断的提出和应用,如FPGA的动态部分重构技术。所谓动态重构是指对于时序变化的数字逻辑系统,其时序逻辑的发生,不是通过调用芯片内不同区域不同逻辑资源的组合来实现,而是通过对具有专门缓存逻辑资源的FPGA,进行局部和全局芯片逻辑的动态重构而快速实现。动态可重构FPGA器件在编程结构上应具有专门的特征,其内部逻辑块和内连线的改变可以通过读取不同的配置比特流文件来实现逻辑重建。动态部分重构是指重新配置FPGA的部分区域,重构过程中,FPGA其余部分的工作状态不受影响。此方式减小了重构范围和单元数目,从而大大缩短了FPGA的重构时间。

本文引用地址:https://www.eepw.com.cn/article/191607.htm应用FPGA动态部分重构功能使硬件设计更加灵活,可用于硬件的远程升级、系统容错和演化硬件以及通信平台设计[1]等。动态部分重构可以通过两种方法实现:基于模块化设计方法(Module-Based Partial Reconfiguration)和基于差别的设计方法(Difference-Based Partial Reconfiguration),本文以基于模块化设计为例说明实现部分重构的方法。

1 FPGA配置原理简介

本文针对Xilinx公司的FPGA进行研究,支持模块化动态部分重构的器件族有Virtex/-II/-E和Virtex-II Pro。

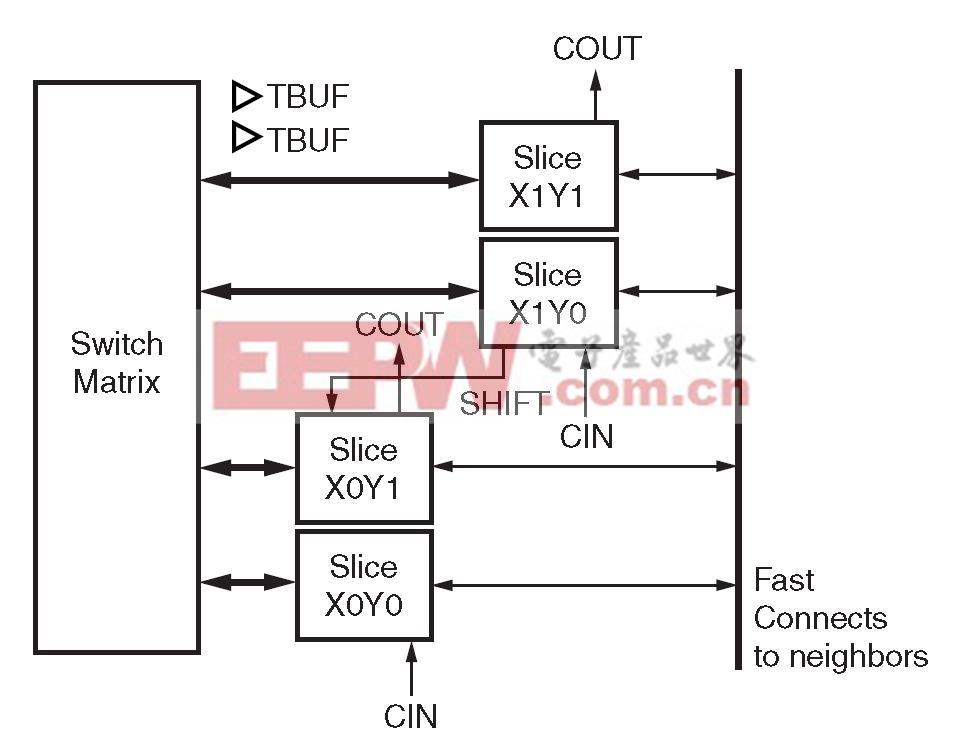

Xilinx公司FPGA是基于SRAM工艺的,包括配置逻辑块(CLBs),输入输出块(IOBs),块RAMs,时钟资源和编程布线等资源[2]。CLBs是构造用户所需逻辑的功能单元,IOBs提供封装引腿与内部信号引线的接口。可编程互连资源提供布线通道连接可配置元件的输入和输出到相应的网络。

存储在内部配置存储器单元中的数值决定了FPGA实现的逻辑功能和互接方式。Virtex FPGA的配置存储器是由配置列(Configuration Columns)组成的,这些配置列以垂直阵列的方式排列,如图1给出了Virtex-E XCV600E器件的配置列构成图。配置存储器可分为五种配置列:Center 列包含四个全局时钟的配置信息;两个IOB 列存储位于器件左边和右边所有IOBs的配置信息;CLB列存储FPGA基本逻辑功能的配置信息;Block SelectRAM Content列存储内部块RAM的配置信息;Block SelectRAM Interconnect列存储内部块RAM间互联的配置信息[3]。

图1 Virtex-E XCV600E的配置列构成及地址

评论