基于FPGA的PCI总线串口卡设计

随着计算机测试技术的飞速发展,越来越多的外部设备通过串口与计算机进行通信,实现信息共享以及设备的集中控制和管理。利用串口进行通信具有结构简单、传输距离远、成本低廉等优点,被广泛应用于各个领域[1]。同时,PCI(Peripheral Component Interconnect)总线是一种高性能32/64位局部总线,最大数据传输速率为132 Mb/s,可同时支持多组外设,数据吞吐量大,是目前应用最广泛、最流行的一种高速同步总线[2]。因此,利用PCI总线实现上位机与外部设备的串口通信,可以提高通信能力。

由于大部分I/O 设备没有PCI总线功能,要实现设备与PCI总线的连接,需要PCI接口芯片、通用异步收发器UART(Universal Asynchronous Receiver Transmitter)等。而目前开发PCI总线与外部设备的串口通信大体上有两种方式:(1)使用专用的芯片,如:PCI专用接口芯片S5920、S5933等;UART专用芯片8250、8251、16450、16550等。使用厂家提供的专用接口芯片,用户可能只使用到它的部分功能,会造成一定的资源浪费,而且专用芯片价格高。(2)使用可编程器件FPGA。使用FPGA较使用专用芯片具有以下优点:一方面用户可以根据需要进行设计,不会浪费资源;另一方面可以将PCI接口、UART都做在一片FPGA内,这样就不需要外接专门的芯片,简化了电路、缩小了体积、提高了系统的可靠性。

1系统硬件设计

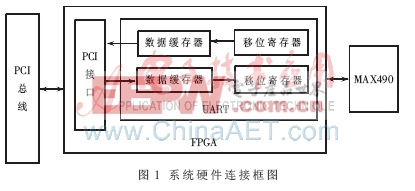

本设计中选用Altera公司的FPGA芯片EP1C6SQ240作为核心器件,完成PCI接口以及UART的设计,实现PCI总线与串口的连接。选用美信公司的MAX490芯片作为电平转换电路。系统的硬件连接框图如图1所示。

数据传输过程:上位机通过PCI总线发送并行数据到UART的数据缓存器中,然后数据经UART的数据缓存器进入UART的移位寄存器进行并串转换后,通过串口传到下位机。反之,下位机通过串口将数据传送到UART的移位寄存器中,进行串并转换,然后进入UART的数据缓存器中,最后传到上位机。

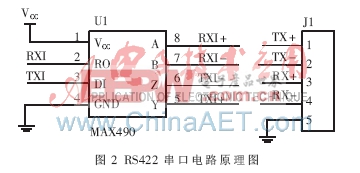

设计中采用,传输距离长、抗干扰能力强的RS422串口。但是规定RS422:逻辑1的电平为-6 V~-2 V;逻辑0的电平为+2 V~+6 V。而FPGA的I/O电平一般为0~3.3 V,二者之间的电平不兼容。为了使二者之间的供电电压保持一致,必须加入电平转换电路。为此选用美信公司的MAX490芯片来实现二者之间的电平转换,其电路原理图如图2所示。

1.1 PCI总线接口

PCI总线接口的功能是将一个不支持 PCI 协议的后端设备接口到PCI 总线上。为了实现PCI总线接口的基本功能,必须完成如下模块的设计:PCI空间配置模块、偶校验模块、地址译码和命令译码模块、设备状态机模块等。PCI总线接口原理框图如图3所示。

评论