基于FPGA的32位ALU软核设计

目前许多FPGA的逻辑资源(LE)都已超过1万门,使得片上可编程系统SOPC已经成为可能。算术逻辑单元ALU应用广泛,是片上可编程系统不可或缺的一部分。利用VHDL语言在FPGA芯片上设计ALU的研究较少,文中选用FPGA来设计32位算术逻辑单元ALU,通过VHDL语言实现ALU的功能。

1 电路总体设计思想

算术逻辑单元ALU采用模块化设计,可以完成32位有符号数和无符号数的加减乘除,还可以实现9种逻辑运算、6种移位操作以及高低字节内容互换等操作。

总体设计图,如图1所示。当you_wu=1时实现有符号数加减乘除运算,否则为无符号数运算。进行有符号数加减运算时c为符号位,无符号数加减运算时c表示进位或借位。加减法运算和逻辑运算结果存于y1。乘运算时,y1放高32位,y2放低32位。除法运算时y1放商,y2放余数。a,b表示两路32位输入数据。

2 主要模块功能分析

算术逻辑单元ALU包含5个模块:控制模块、逻辑模块、加减法模块、乘法模块和除法模块。控制模块比较简单,即1个2线~4线译码器,完成其他模块的控制与选择。当ctr=00时完成逻辑运算,ctr=01时完成加减法运算,ctr=10时完成乘法运算,ctr=11时完成除法运算。

2.1 逻辑运算模块

本模块实现与、或、非、与非、或非、异或、同或、逻辑左移、逻辑右移、算术左移、算术右移、逻辑循环左移、逻辑循环右移以及高低半字(16位)分别取反和高低字内容互换等操作。用1个case语句即可实现上述全部功能。

2.2 加减法模块

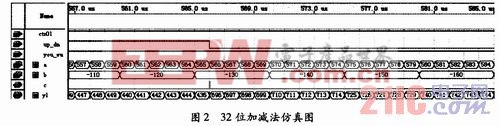

加减法模块可根据需要完成32位有符号数和无符号数的加减运算,在程序开始时先判断所要进行的运算有无符号数,对于有符号数,用符号位将两组数扩展为33位二进制数,否则用0扩展为33位二进制数,其中减法运算采用补码实现,所以整个程序只有加法运算。程序只占用68个逻辑资源(LE),非常节省资源,而且速度很快,是一种优化设计。仿真图如图2所示。

评论